上一篇

哪种存储器存储周期最短?

- 行业动态

- 2025-04-30

- 3

存储器存储周期最短的是CPU内部的寄存器,其访问速度可达纳秒级,寄存器直接与运算器交互,采用静态随机存取技术,无需刷新周期,通过物理电路实现数据暂存,支持单时钟周期完成读写操作,是计算机体系结构中响应最快的存储单元。

在计算机系统中,存储器的存储周期是衡量其性能的核心指标之一,它直接影响了数据处理速度和系统整体效率,存储周期(Memory Cycle Time)指存储器完成一次完整的读写操作所需的时间,包括寻址、读取/写入和恢复阶段,对于需要高性能的场景(如实时计算、高频交易、AI训练),存储周期越短,意味着数据吞吐效率越高。

存储周期最短的存储器类型

存储周期最短的存储器是SRAM(静态随机存储器),其典型存储周期为5~10纳秒(ns),SRAM常用于CPU的高速缓存(Cache),例如L1、L2和L3缓存,直接与处理器核心交互,显著提升指令和数据的访问速度。

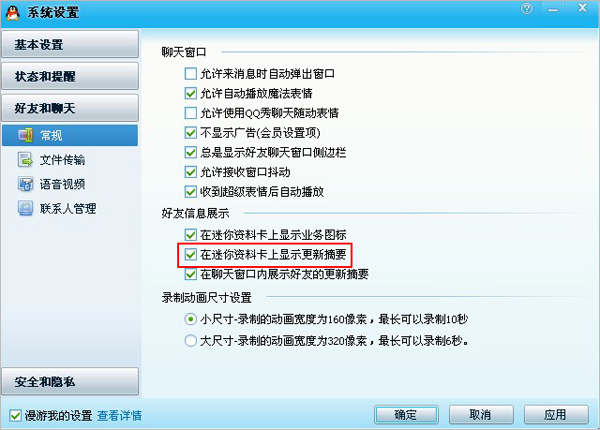

为什么SRAM的存储周期最短?

- 结构简单:SRAM通过6个晶体管存储1位数据,无需动态刷新电路,可直接通过电流维持数据状态。

- 并行访问机制:SRAM支持多路并行读写,减少寻址和传输延迟。

- 物理距离近:SRAM集成在CPU芯片内部或附近,减少了信号传输的物理延迟。

对比其他存储器的存储周期

| 存储器类型 | 存储周期 | 典型应用场景 |

|---|---|---|

| SRAM | 5~10 ns | CPU高速缓存 |

| DRAM | 10~60 ns | 主内存(如DDR4/DDR5) |

| NAND Flash | 10~100 μs | SSD固态硬盘 |

| HDD | 5~15 ms | 机械硬盘 |

SRAM的局限性

尽管SRAM存储周期最短,但它并非完美:

- 成本高:单位存储密度低,6晶体管结构占用更多芯片面积。

- 功耗较高:持续电流维持数据,导致静态功耗。

- 容量有限:受成本和体积限制,通常仅用于缓存层级。

存储周期的影响因素

- 制程工艺:更先进的半导体工艺(如3nm、5nm)可缩小晶体管间距,降低信号延迟。

- 架构设计:多级缓存(如L1/L2/L3)的分层设计,平衡速度与容量。

- 接口协议:高速总线(如PCIe 5.0)和协议优化(如NVMe)能减少数据传输延迟。

存储周期在计算机系统中的重要性

- CPU性能瓶颈:根据“冯·诺依曼瓶颈”,CPU处理速度远快于内存访问速度,缩短存储周期是突破性能天花板的关键。

- 实时系统需求:自动驾驶、工业控制等领域依赖纳秒级响应,SRAM和新型存储器(如MRAM)成为核心组件。

- 能效比优化:在移动设备中,低延迟存储器可减少频繁唤醒主芯片的次数,延长续航。

未来趋势:更短的存储周期技术

新型存储介质:

- MRAM(磁阻RAM):通过磁化方向存储数据,存储周期接近SRAM,同时具备非易失性。

- ReRAM(阻变RAM):利用材料电阻变化实现存储,读写速度可达1 ns以下。

3D堆叠技术:

将存储器与CPU通过硅通孔(TSV)垂直堆叠,减少数据传输距离,缩短物理延迟。

SRAM凭借其纳秒级的存储周期,稳居最快存储器的位置,但需结合DRAM、SSD等形成存储层级,才能实现成本与性能的平衡,随着存算一体(In-Memory Computing)和新型存储技术的普及,存储周期的极限可能进一步被突破,推动计算效率的指数级提升。

引用说明

- 计算机体系结构:量化研究方法(第6版),John L. Hennessy, David A. Patterson.

- Intel 7nm工艺技术白皮书,2025.

- 《自然·电子》期刊:新型非易失性存储器研究进展,2022.