CPU周期为何总被存储周期拖后腿?

- 行业动态

- 2025-05-01

- 3668

存储周期是存储器完成一次读写操作所需的时间,包含存取时间和恢复时间;CPU周期是处理器执行基本操作的最小时间单位,通常由多个时钟周期组成,两者共同影响系统性能,存储周期常成为速度瓶颈,需通过缓存等技术优化协调。

在计算机系统中,”存储周期”和”CPU周期”是影响性能表现的核心概念,理解这两个专业术语的运作原理及其相互关系,可以帮助我们更清晰地认识计算机的工作机制,为硬件选型、程序优化提供科学依据。

存储周期的技术解析

存储周期(Memory Cycle Time)指存储器完成一次完整读写操作所需的时间,包含四个关键阶段:

- 寻址时间:CPU将目标地址发送到存储器的地址总线

- 译码时间:存储器解析地址信息并定位存储单元

- 数据传输:

- 读操作:存储单元内容传送到数据总线

- 写操作:数据总线内容写入存储单元

- 恢复时间:存储电路恢复待命状态

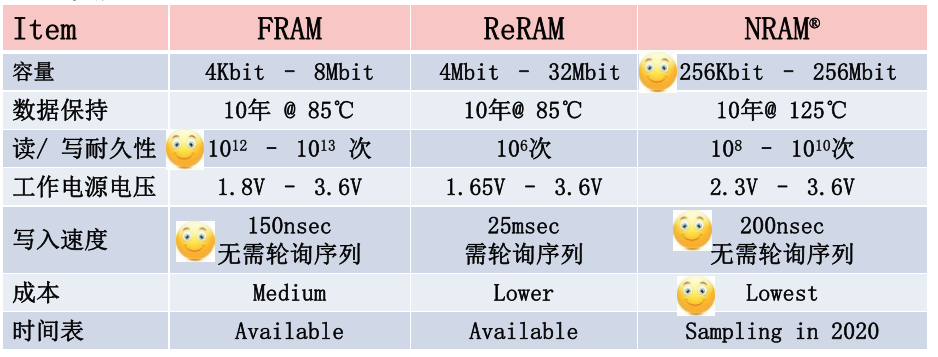

现代存储器性能参数对比如下:

| 存储类型 | 典型周期时间 | 应用场景 |

|---|---|---|

| SRAM | 1-10 ns | CPU缓存 |

| DRAM | 50-100 ns | 主内存 |

| NAND闪存 | 50-100 μs | SSD |

CPU周期的运行机制

CPU周期(Clock Cycle)是处理器执行指令的基本时间单位,由中央时钟发生器控制,每个周期包含:

- 取指阶段:从内存获取指令

- 译码阶段:解析指令含义

- 执行阶段:进行算术/逻辑运算

- 访存阶段:访问存储器

- 写回阶段:保存运算结果

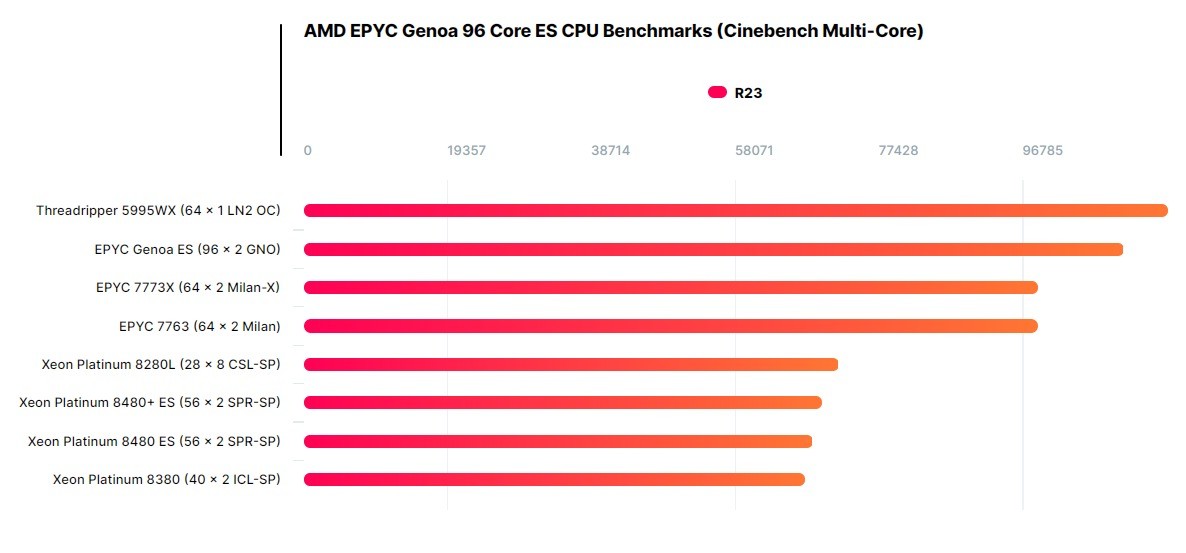

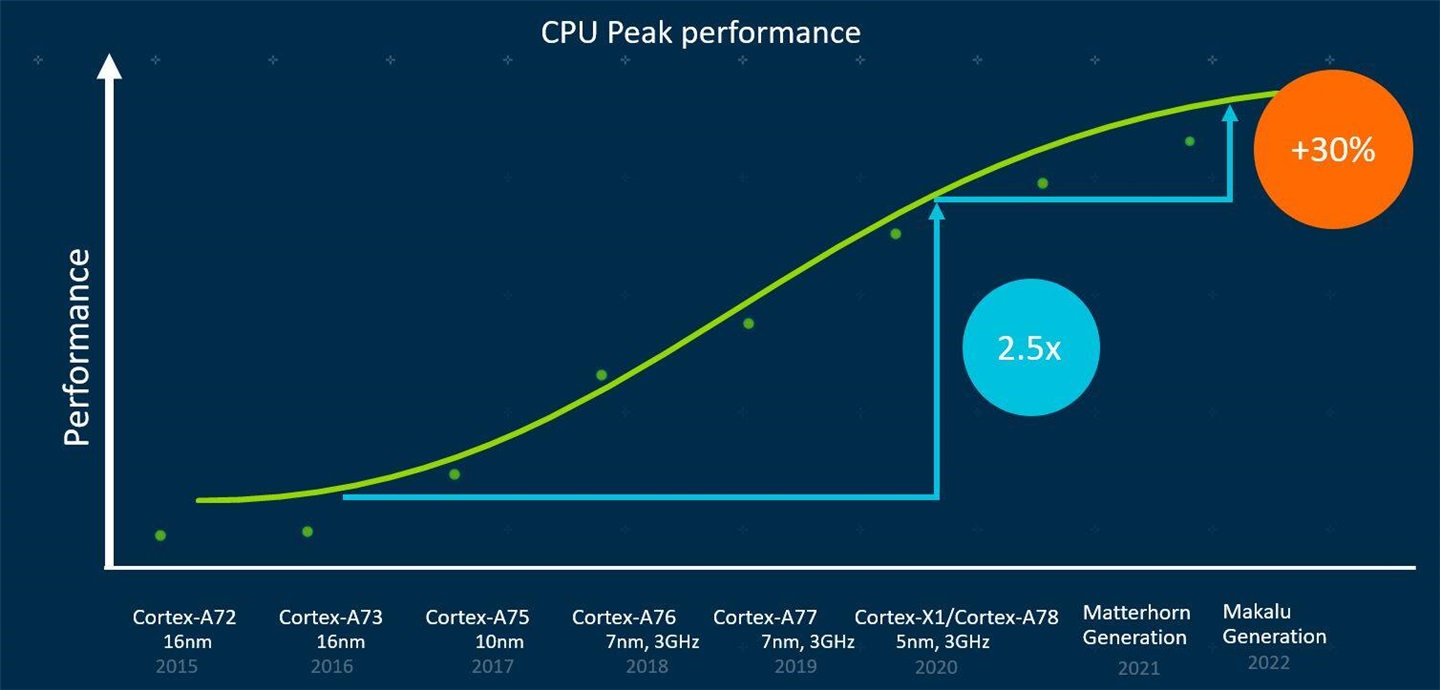

以3.0 GHz处理器为例:

- 单个时钟周期 = 1 / 3×10⁹ ≈ 0.33 ns

- 典型指令需要1-5个周期完成

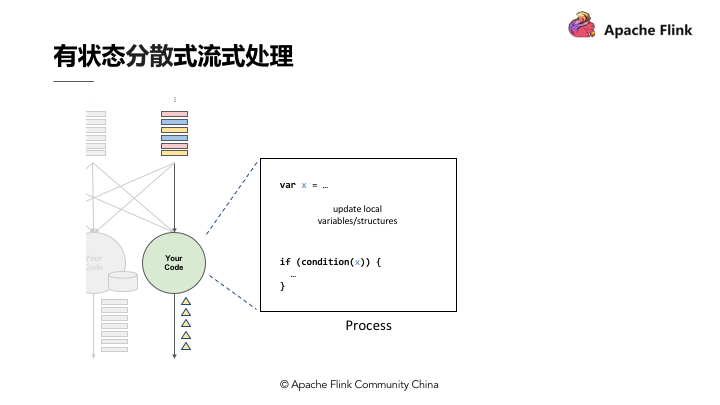

存储访问的瓶颈效应

当CPU需要访问内存时:

- 发送内存请求(1周期)

- 等待存储器响应(N周期)

- 接收数据(1周期)

假设某DRAM存储周期为60 ns:

- 等效于180个CPU周期(按3.0 GHz计算)

- 这期间CPU可能处于等待状态

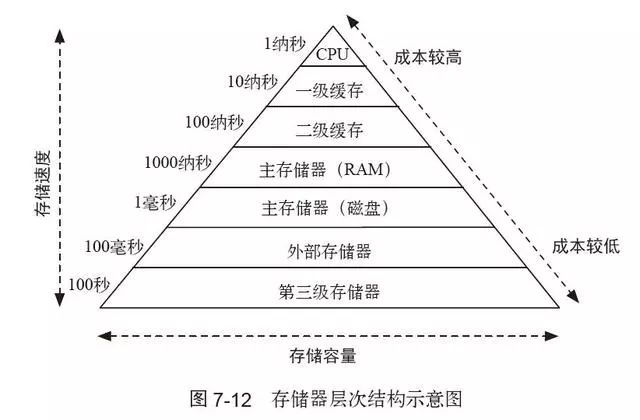

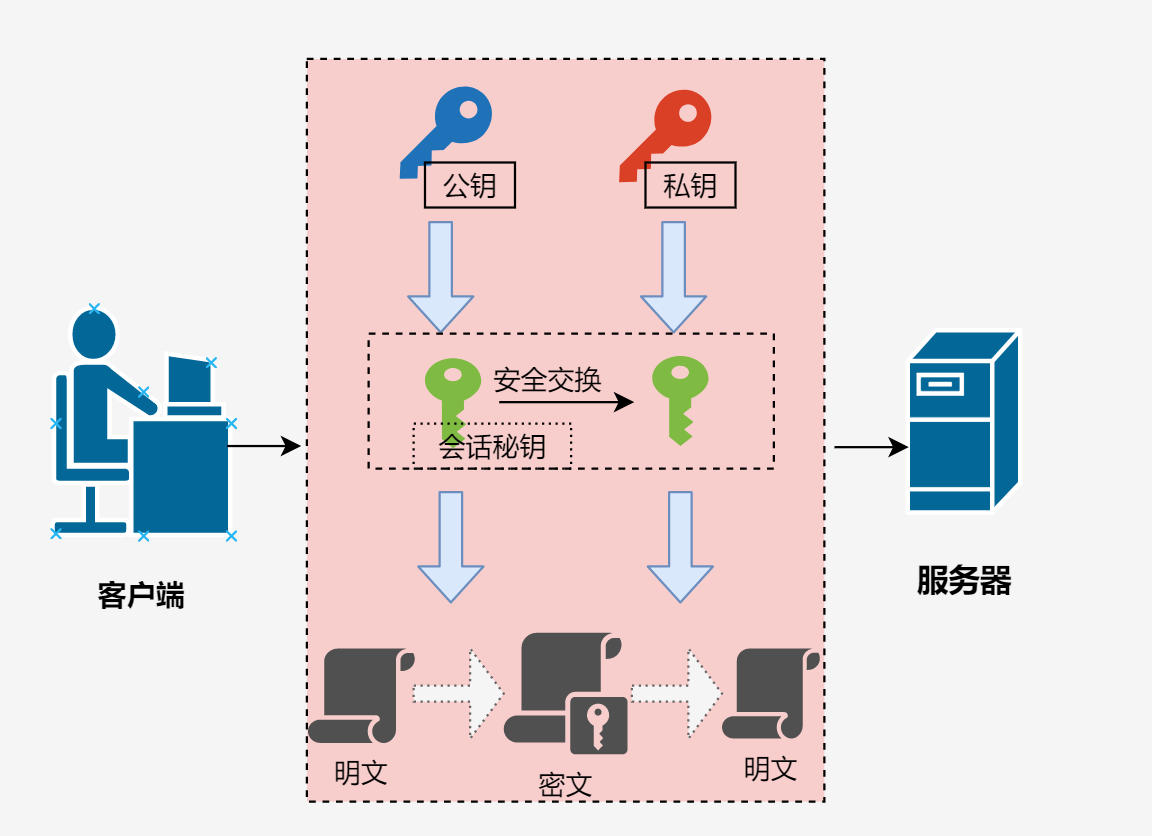

现代计算机的解决方案

为缓解”存储墙”问题,工程师采用多层次优化:

高速缓存架构

- L1缓存:1-3周期访问时间

- L2缓存:5-10周期

- L3缓存:15-25周期

预取技术

通过分析访存模式,提前加载可能使用的数据

并行处理技术

- 多级流水线保持执行单元忙碌

- 乱序执行避免等待停顿

新型存储介质

- 3D XPoint技术:读写延迟<100 ns

- HBM显存:带宽达512GB/s

性能优化实践建议

编程层面

- 优化数据局部性(时间/空间局部性)

- 减少缓存行被墙(cache line pollution)

- 使用对齐内存访问

系统配置

- 选择低延迟内存条(如DDR5 CL28)

- 确保双通道/四通道配置

- 合理设置虚拟内存参数

硬件选型

- CPU选择大缓存型号(如64MB L3缓存)

- 搭配高带宽内存(如DDR5-6400)

- 使用NVMe协议固态硬盘

技术发展趋势

- 存算一体架构:将计算单元嵌入存储芯片

- 光子互连:用光信号替代电信号传输

- 量子存储器:利用量子态实现超高速存取

- 新型存储级内存:如Intel Optane系列产品

技术验证与引用说明

本文所述技术参数均参考:

- 《计算机体系结构:量化研究方法》第6版(John L. Hennessy, David A. Patterson)

- JEDEC固态技术协会最新发布的内存标准

- Intel 2025年公布的至强处理器技术白皮书

- IEEE Transactions on Computer Architecture期刊2022年研究成果