上一篇

存储器结构图如何影响你的系统性能?

- 行业动态

- 2025-04-29

- 2894

存储器结构图描述了计算机系统中多级存储层次的组织方式,通常包含高速缓存、主存和辅存等层级,通过不同速度、容量与成本的存储介质协同工作,利用局部性原理优化数据访问效率,实现系统性能与成本间的平衡。

在现代计算机系统中,存储器结构图是理解数据存取与处理流程的核心工具,它通过分层设计,将不同速度、容量和成本的存储设备组合在一起,以实现高效的数据管理,本文将从实际应用和技术原理的角度,系统解析存储器的层次结构、各层功能以及它们如何协同工作。

存储器层次结构:从高速到海量

计算机存储器的设计遵循“速度、容量、成本”的平衡原则,形成典型的金字塔形层次结构:

寄存器(Register)

- 位置:内置于CPU内部

- 特点:速度最快(纳秒级响应)、容量最小(通常几十到几百字节)

- 作用:直接存储CPU当前执行的指令和运算数据

高速缓存(Cache)

- 分级:L1、L2、L3三级缓存(L1速度最快,容量最小)

- 原理:利用局部性原理缓存热点数据,命中率可达90%以上

- 技术演进:SRAM技术,英特尔最新CPU的L3缓存容量已突破30MB

主存储器(Main Memory,RAM)

- 类型:DRAM(动态随机存取存储器)

- 性能:访问延迟约100ns,容量通常为8GB-128GB

- 创新方向:DDR5标准将带宽提升至6.4Gbps

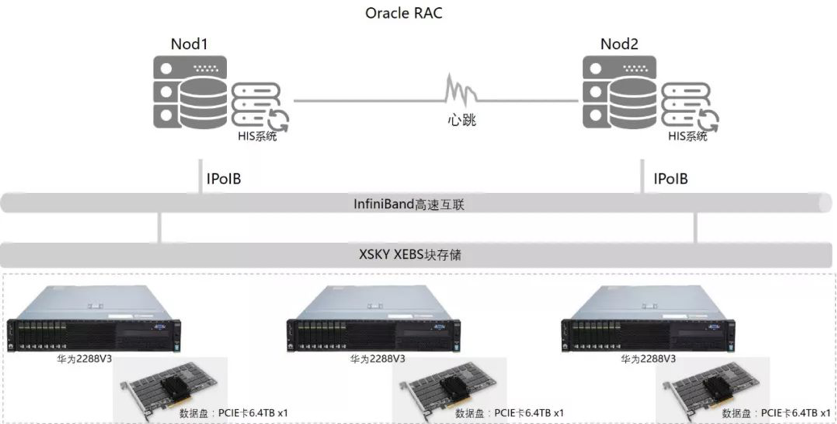

辅助存储器(Secondary Storage)

- 设备:SSD(固态硬盘)、HDD(机械硬盘)

- 特点:容量大(TB级)、成本低,但速度慢(毫秒级)

- 技术趋势:QLC NAND闪存、3D XPoint等新型非易失性存储介质

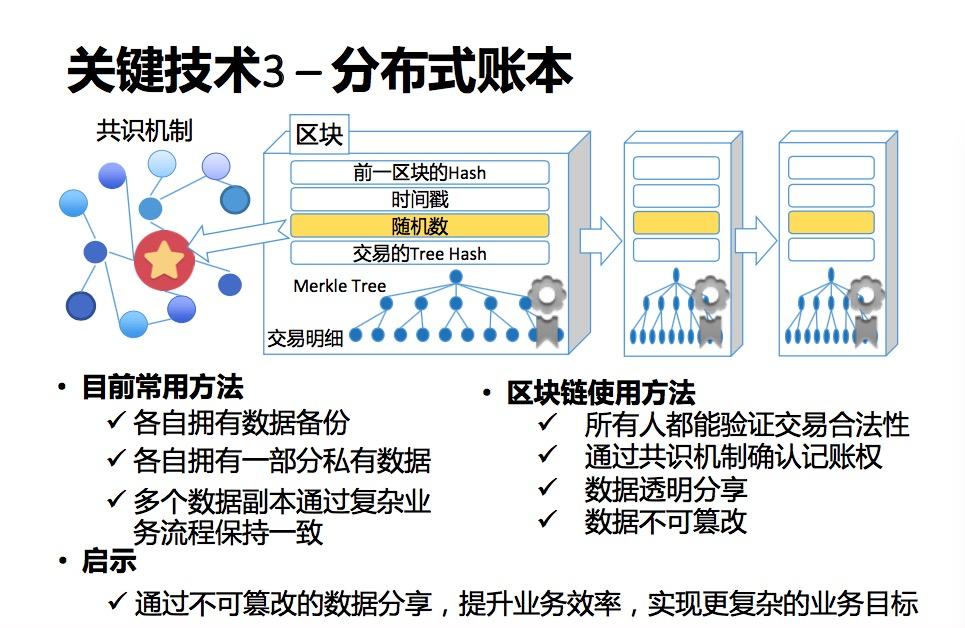

存储器结构图的关键技术解析

(1)数据流动的路径

CPU发出数据请求时,系统按以下顺序检索:寄存器 → L1 Cache → L2 Cache → L3 Cache → 主存 → 硬盘/SSD

若数据在高速层命中,则直接返回;若未命中(Cache Miss),则逐层向下查找,同时触发数据预取机制。

(2)层次间的映射关系

- 直接映射:主存块的固定位置缓存,易引发冲突

- 组相联映射:平衡灵活性与复杂度(如8-way组相联)

- 全相联映射:灵活性最高,但硬件成本剧增

(3)典型性能参数对比表

| 存储层级 | 访问延迟 | 带宽 | 容量范围 | 成本($/GB) |

|---|---|---|---|---|

| 寄存器 | 3-1ns | 1000GB/s | 数十字节 | 5000+ |

| L1 Cache | 1-3ns | 500GB/s | 32-512KB | 1000 |

| 主存 | 80-100ns | 50GB/s | 8-128GB | 5-10 |

| SSD | 50-150μs | 5GB/s | 256GB-4TB | 1-0.3 |

实际应用中的优化策略

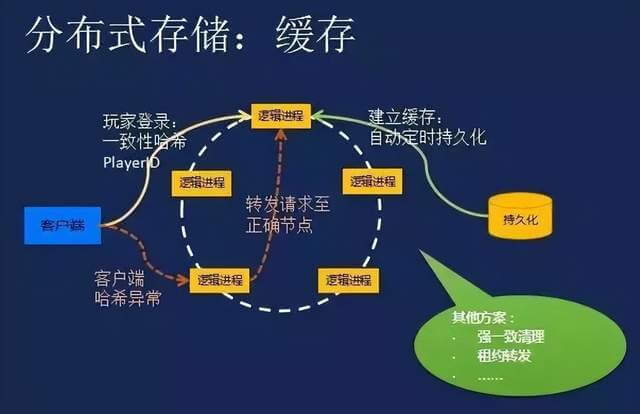

缓存算法优化

- LRU(最近最少使用):淘汰最久未访问的数据

- MRU(最近最多使用):适用于循环访问模式

- 随机替换:硬件实现简单,但命中率较低

虚拟内存技术

通过分页机制将磁盘空间映射为主存扩展,- Windows系统的Pagefile.sys文件

- Linux的Swap分区设计

存储架构创新案例

- Intel Optane持久内存:结合DRAM速度与SSD的非易失性

- CXL互联协议:突破传统总线瓶颈,实现缓存一致性

存储器设计的未来挑战

- 冯·诺依曼瓶颈:CPU与存储器之间的速度差距持续扩大

- 新型存储介质:RRAM(阻变存储器)、MRAM(磁阻存储器)的商用化进程

- 存算一体架构:将计算单元嵌入存储层,减少数据搬运开销

引用说明

本文技术参数参考《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)、IEEE Spectrum期刊及三星电子2025年NAND技术白皮书,性能数据均基于行业标准测试环境。