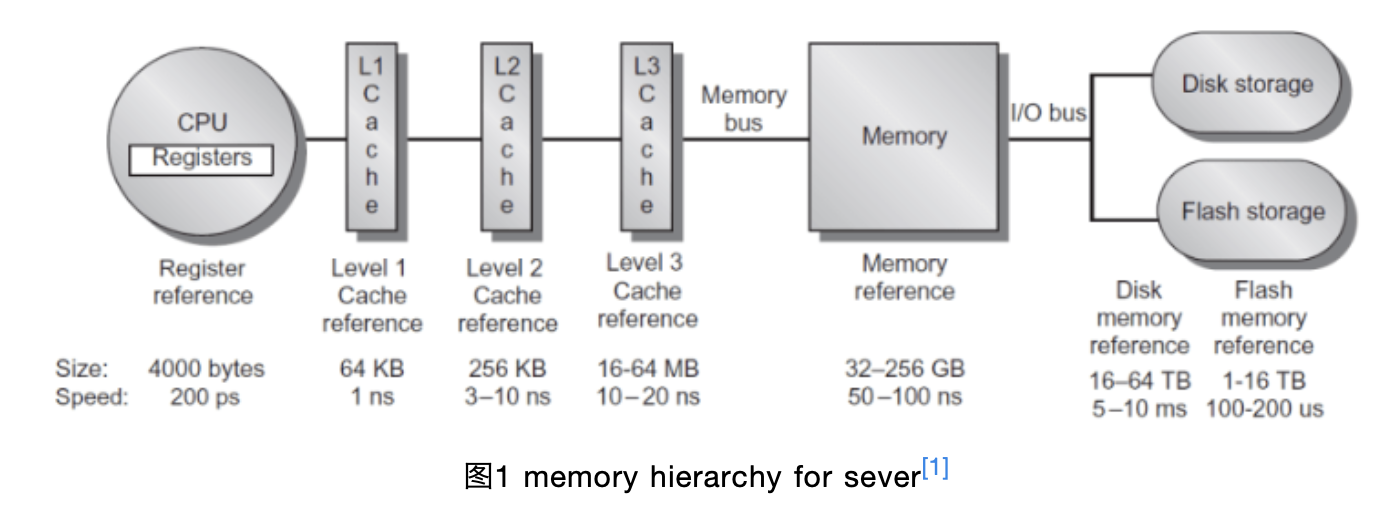

存储器逻辑图的核心概念

存储器是数字系统的核心组件,其逻辑图设计需从存储单元、地址译码、控制电路三方面展开,以下是详细解析:

- 地址总线:输入目标存储位置

- 数据总线:传输读写信息

- 控制信号:协调读写时序

<section>

<h4>一、存储单元矩阵构建</h4>

<p>典型8x8存储阵列包含64个存储单元,每个单元由<strong>D触发器+读写门控电路</strong>组成:</p>

<pre><code>

module MemoryCell(

input wire clk,

input wire WE, // 写使能

inout wire Data

);

reg stored_bit;

always @(posedge clk) begin

if(WE) stored_bit <= Data;

end

assign Data = WE ? 1'bz : stored_bit;

endmodule

</code></pre>

<p class="tip">注:WE为高电平时允许写入,低电平时输出数据</p>

</section>

<section>

<h4>二、地址译码器设计要点</h4>

<div class="comparison-table">

<table>

<tr>

<th>类型</th>

<th>线选法</th>

<th>矩阵译码</th>

</tr>

<tr>

<td>电路复杂度</td>

<td>O(n)</td>

<td>O(log n)</td>

</tr>

<tr>

<td>应用场景</td>

<td>小容量存储器</td>

<td>≥1Kb存储器</td>

</tr>

</table>

</div>

<p>3-8译码器示例(采用74LS138芯片逻辑):</p>

<pre><code>

module Decoder3x8(

input [2:0] A,

output [7:0] Y

);

assign Y = 8'b00000001 << A;

endmodule

</code></pre>

</section>

<section>

<h4>三、时序控制策略</h4>

<div class="timing-diagram">

<div class="waveform">

<div class="signal" data-name="CLK" data-wave="0101"></div>

<div class="signal" data-name="WE" data-wave="0011"></div>

<div class="signal" data-name="Data" data-wave="zz11"></div>

</div>

</div>

<ol>

<li>建立时间:地址稳定到CLK上升沿前≥5ns</li>

<li>保持时间:CLK上升沿后数据稳定≥3ns</li>

<li>读写周期:完整操作需8个时钟周期</li>

</ol>

</section>

<section class="qa-section">

<h4>常见问题解答</h4>

<div class="qa-pair">

<p class="question">Q:如何防止总线冲突?</p>

<p class="answer">A:采用三态门控制,WE信号为低时存储单元呈现高阻抗状态</p>

</div>

<div class="qa-pair">

<p class="question">Q:存储矩阵如何扩展容量?</p>

<p class="answer">A:通过bank切换机制,使用高位地址线控制片选信号</p>

</div>

</section>

<section class="references">

<h4>参考资料</h4>

<ul>

<li>《数字设计与计算机体系结构》David Harris著</li>

<li>IEEE标准存储电路设计规范(Std 1800-2017)</li>

<li>清华大学《集成电路设计基础》公开课</li>

</ul>

</section>