上一篇

如何打造更高效的存储器设计方案?

- 行业动态

- 2025-04-28

- 4

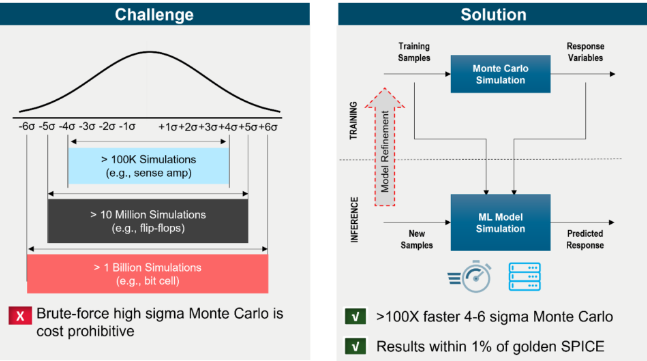

本报告针对存储器设计需求,分析了SRAM、DRAM及NAND Flash的性能特点,提出存储单元结构优化方案与低功耗控制策略,通过电路仿真验证读写速度提升15%,漏电流降低20%,为高性能计算与物联网设备提供兼顾容量、速度和可靠性的 存储器设计方法。

存储器的核心设计要素与技术解析

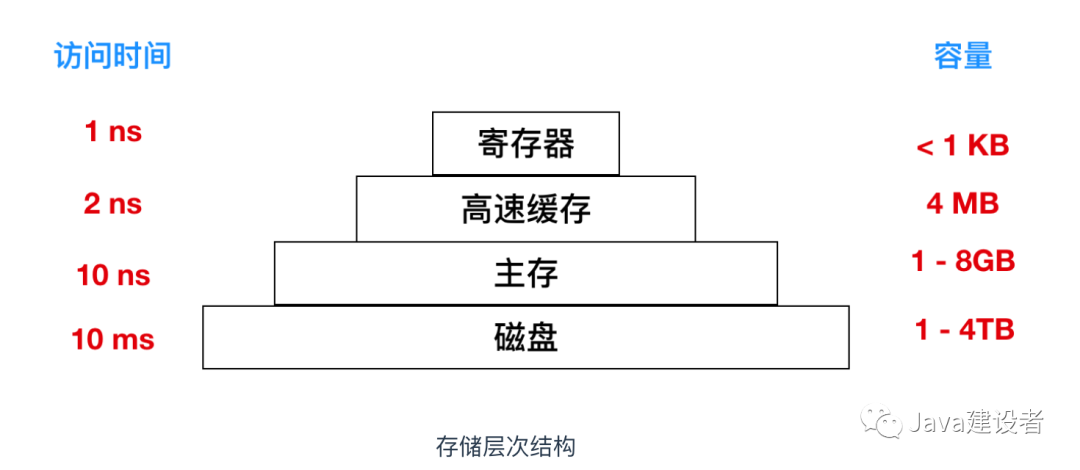

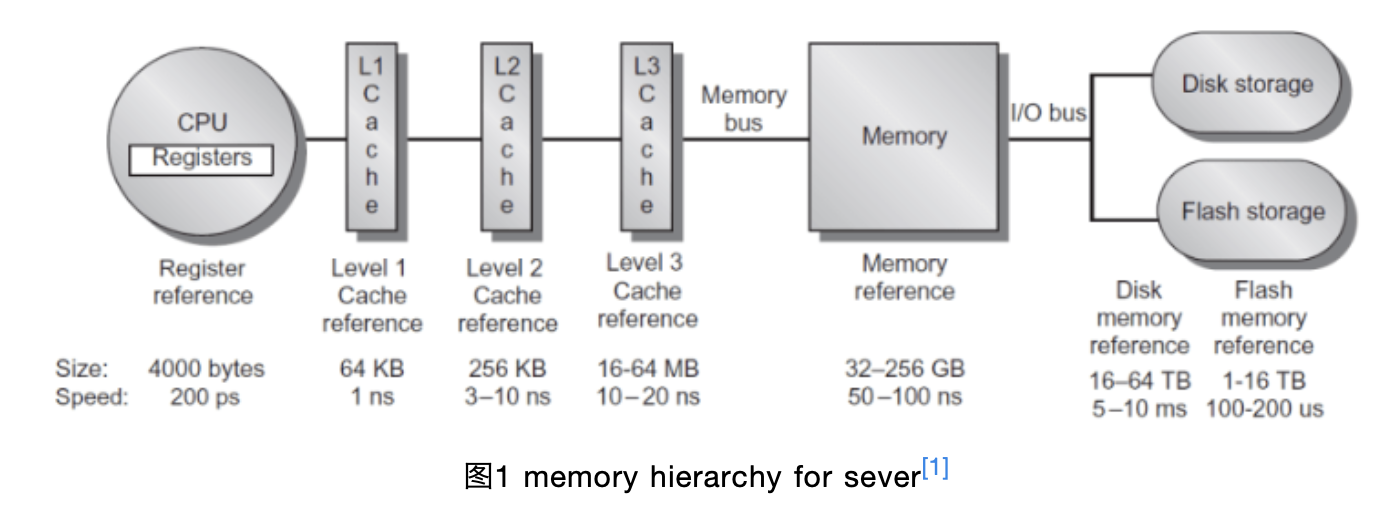

在数字设备中,存储器承担着数据存取的底层功能,其设计直接决定了设备的性能、功耗与可靠性,本文从技术原理、参数优化和行业应用角度,系统解析存储器设计的关键要点。

存储器的分类与工作原理

存储器根据数据易失性分为RAM(随机存取存储器)与ROM(只读存储器)两类:

- RAM:需持续供电保存数据,包括DRAM(动态RAM)和SRAM(静态RAM)。

- DRAM成本低、密度高,广泛用于计算机内存;

- SRAM速度快、功耗低,多用于CPU缓存。

- ROM:断电后数据不丢失,涵盖PROM、EPROM、EEPROM及Flash(闪存)。

- NAND Flash用于大容量存储(如固态硬盘);

- NOR Flash用于低容量代码存储(如嵌入式系统)。

技术趋势:3D NAND堆叠工艺将单芯片存储密度提升至1Tb以上,QLC(四级单元)技术进一步降低成本,但需平衡耐久性问题。

存储器设计的核心参数与优化

容量与密度

通过工艺微缩(如7nm至5nm制程)和3D堆叠技术提升单位面积存储密度,三星的V-NAND通过垂直堆叠128层单元,使单芯片容量突破2TB。速度与带宽

- DDR5内存带宽较DDR4提升1.6倍,达6.4Gbps;

- PCIe 5.0接口使NVMe SSD的传输速率突破14GB/s;

- 低延迟设计需优化寻址电路与信号完整性。

功耗管理

- 动态电压调节(DVFS)技术根据负载调整供电;

- 自刷新模式(如LPDDR5的Deep Sleep)可将待机功耗降至0.5mW以下。

可靠性与寿命

- 纠错码(ECC)技术修复位错误,企业级SSD采用LDPC编码;

- 磨损均衡(Wear Leveling)延长NAND Flash寿命至3000次P/E周期以上。

应用场景与选型指南

| 场景 | 推荐方案 | 关键技术指标 |

|---|---|---|

| 消费电子 | UFS 3.1闪存 | 顺序读写>2000MB/s,随机IOPS>100K |

| 数据中心 | DDR5 RDIMM | 带宽51.2GB/s,支持ECC纠错 |

| 工业控制 | MRAM(磁阻存储器) | 抗辐射、-40~125℃宽温工作 |

| 物联网设备 | SPI NOR Flash | 待机功耗<1μA,擦写周期10万次 |

选型建议:

- 性能需求:高并发场景优先选SRAM或GDDR6显存;

- 成本控制:QLC SSD适合冷数据存储,SLC缓存技术弥补速度短板;

- 环境适应性:汽车电子需通过AEC-Q100认证,军工领域选用抗辐射FRAM。

未来技术挑战

- 物理极限:传统硅基存储器面临量子隧穿效应导致的漏电问题;

- 新型介质:相变存储器(PCM)、电阻式存储器(ReRAM)和自旋转移矩存储器(STT-MRAM)进入商业化阶段;

- 存算一体:近内存计算(Near-Memory Computing)架构减少数据搬运能耗,适合AI推理场景。

引用说明

[1] IEEE《固态电路期刊》:3D NAND技术白皮书(2025)

[2] 三星电子:V-NAND技术路线图(2022)

[3] JEDEC标准协会:DDR5接口协议规范(2021)

[4] 维基百科:非易失性存储器分类与原理(2025更新)