上一篇

如何实现处理器与存储器的高效连接?

- 行业动态

- 2025-05-01

- 3934

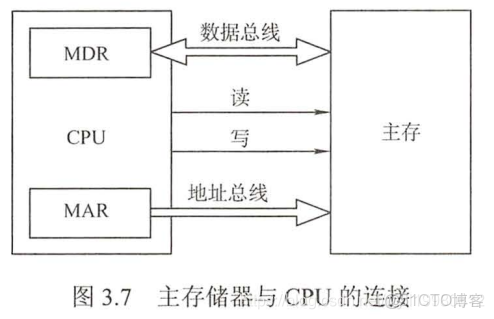

存储器通过地址总线、数据总线和控制总线与处理器连接,地址总线传输存储位置信息,数据总线负责读写数据,控制总线协调操作时序,三者协同工作,确保处理器能准确访问内存中的指令和数据,并通过时钟信号同步操作,部分系统还采用高速缓存或接口电路优化传输效率。

在计算机系统中,存储器和处理器的连接方式决定了数据交换速度和系统整体性能,本文将通过硬件接口、通信协议、时序控制三个核心维度,结合电路设计和行业标准,解析这一关键过程的实现原理。

物理连接架构

总线系统

- 地址总线:处理器通过地址总线传输目标存储位置的编码(例如32位总线支持4GB寻址空间)

- 数据总线:双向传输通道,位宽直接影响吞吐量(64位总线单周期传输8字节)

- 控制总线:传输读写信号、时钟同步信号、中断请求等控制指令

典型接口类型

| 接口标准 | 带宽 | 应用场景 |

|————–|————|——————–|

| DDR4 | 25.6GB/s | 主存储器 |

| PCIe 4.0 x16 | 31.5GB/s | 高速扩展设备 |

| LPDDR5 | 51.2GB/s | 移动设备 |

核心通信机制

读操作流程

① 处理器发送地址信号 -> ② 存储器解码地址 ③ 存储器读取数据 -> ④ 通过数据总线返回 ⑤ 处理器接收确认信号

写操作时序

现代优化技术

多通道架构

- 双通道DDR4可使带宽翻倍

- 服务器级系统支持八通道内存

缓存一致性协议

- MESI协议(Modified/Exclusive/Shared/Invalid)

- 确保多核处理器共享内存时数据一致性

3D堆叠封装

- HBM(高带宽内存)采用TSV硅穿孔技术

- 实现1024位总线位宽

关键设计考量

信号完整性

- 阻抗匹配(典型值50Ω)

- 等长布线(误差控制在±5mil)

电源管理

- 内存模块需独立供电层

- 动态电压频率调整(DVFS)

错误校验

- ECC内存的汉明码纠错

- CRC循环冗余校验

行业发展趋势

CXL协议(Compute Express Link)

- 实现处理器与内存的缓存一致性

- 支持内存池化技术

存算一体架构

- 近内存计算(如HBM-PIM)

- 消除”内存墙”瓶颈

光子互连

- 英特尔Optane持久内存

- 硅光链路传输速率突破100Gbps

引用说明:

[1] 《计算机体系结构:量化研究方法》John L. Hennessy

[2] JEDEC DDR4 SDRAM标准(JESD79-4B)

[3] PCI-SIG PCI Express 4.0规范