抽象机 物理机

- 物理机

- 2025-08-11

- 21

基础概念界定

抽象机的本质特征

抽象机并非物理实体,而是通过指令集架构(Instruction Set Architecture, ISA)定义的逻辑规范,其核心目标是为上层软件提供统一且可预测的执行环境,典型特征包括:

| 属性 | 描述 |

|————–|———————————————————————-|

| 虚拟性 | 独立于具体硬件实现,同一ISA可适配多种物理芯片 |

| 规范性 | 严格定义寄存器数量、指令格式、内存寻址方式等参数 |

| 隔离性 | 隐藏物理器件差异(如缓存机制、流水线级数),呈现理想化计算模型 |

| 可扩展性 | 支持新增指令集向后兼容(如x86-64扩展AVX指令集) |

| 语义完整性| 确保每条指令的行为具有唯一确定性,消除歧义 |

以x86架构为例,Intel和AMD生产的不同处理器均遵循相同的x86 ISA规范,使得针对该架构编译的程序能在两类芯片上无缝运行,这种抽象机制极大提升了软件生态的通用性。

物理机的实体构成

物理机是由半导体材料构成的电子装置,其物理特性直接影响系统性能边界,关键组件包含:

| 层级 | 典型组件 | 功能作用 |

|————–|—————————|—————————————|

| 核心单元 | CPU核心 | 执行算术逻辑运算、控制流程跳转 |

| 存储系统 | L1/L2/L3缓存 | 高速暂存区加速数据访问 |

| 互联网络 | 片上总线、HyperTransport | 协调各模块间数据传输 |

| 外围设备 | 内存控制器、PCIe接口 | 连接外部存储器与外设 |

| 辅助电路 | 电压调节模块、散热系统 | 保障稳定运行环境 |

现代CPU采用超大规模集成电路技术,单个芯片集成数十亿晶体管,例如Apple M1芯片将CPU、GPU、神经网络引擎整合在同一封装内,但其对外仍表现为ARMv8架构的抽象机接口。

协同工作机制

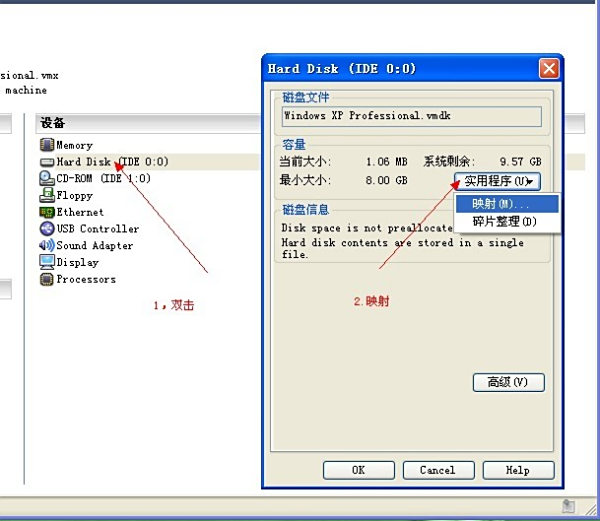

翻译执行流程

抽象机与物理机的协作遵循”编译-链接-加载-执行”的经典路径:

- 源代码编译:高级语言经编译器转化为抽象机指令(机器码)

- 二进制转换:汇编器将汇编代码转为目标ISA的机器码

- 动态翻译:若存在跨架构需求(如Java JVM),需通过解释器/即时编译器完成二次转换

- 物理执行:最终指令由物理机的取指→解码→执行单元逐条处理

此过程中,抽象机承担着”语言桥梁”角色,使软件开发者无需关注底层电路细节,而物理机则专注于高效执行指令,其微架构设计(如分支预测、乱序执行)直接影响实际性能表现。

异常处理机制

当物理机检测到错误状态(如页缺失、除零错误)时,会触发特殊中断向量,此时抽象机层面的操作系统内核接管控制权,完成以下操作:

- 保存现场上下文(程序计数器、寄存器状态)

- 定位异常原因并调用对应处理程序

- 恢复执行环境后继续运行

这种分层处理机制既保证了系统安全性,又维护了抽象机的一致性视图。

关键技术差异对比

| 维度 | 抽象机 | 物理机 | 备注 |

|---|---|---|---|

| 存在形式 | 逻辑规范文档 | 实体硅片 | 前者无形,后者可见 |

| 设计目标 | 最大化软件移植性 | 追求最高吞吐量/能效比 | 矛盾统一体 |

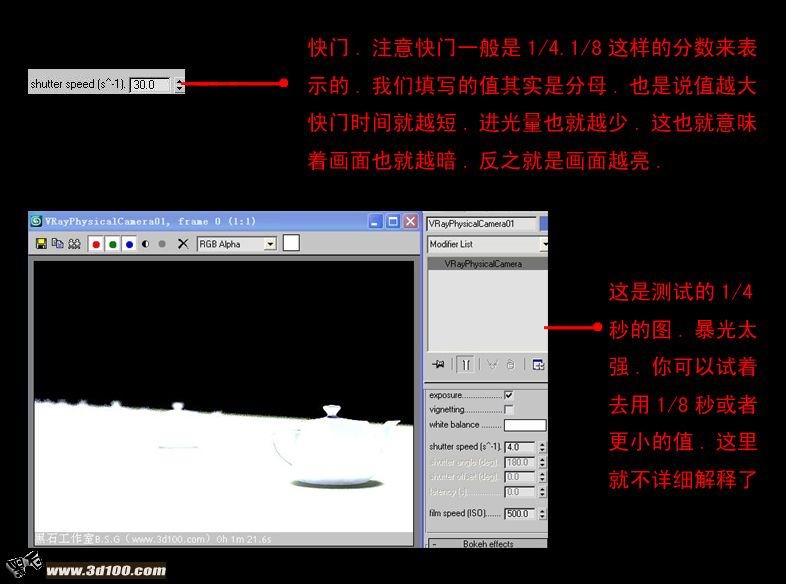

| 更新周期 | 数年迭代一次(新版ISA发布) | 每年工艺升级(制程缩小) | Moore定律驱动 |

| 资源管理 | 虚拟地址空间(理论无限大) | 实际物理内存容量限制 | 虚拟内存技术缓解矛盾 |

| 错误容忍度 | 强制类型检查(编译期捕获错误) | 运行时异常频发(需容错设计) | 软硬件协同可靠性保障 |

| 性能瓶颈 | 指令集复杂度 | 主频上限、发热限制 | Dennard缩放法则失效后的挑战 |

| 安全边界 | 沙箱机制隔离反面代码 | Spectre/Meltdown类硬件破绽 | 近年安全问题焦点转移 |

典型应用场景分析

嵌入式系统领域

在物联网设备中,常采用精简指令集(RISC)架构的抽象机设计,例如ARM Cortex-M系列:

优势:低功耗模式丰富,适合电池供电场景

️ 挑战:浮点运算单元可选配,需谨慎选择开发工具链

实践建议:优先使用CMSIS标准库,避免直接操作物理寄存器

高性能计算场景

超级计算机采用定制ISA+专用加速器的组合方案:

技术路线:NVIDIA CUDA架构(GPGPU加速)+ OpenPOWER处理器

性能突破:通过SIMD向量指令并行处理矩阵运算

️ 瓶颈应对:混合精度计算降低内存带宽需求

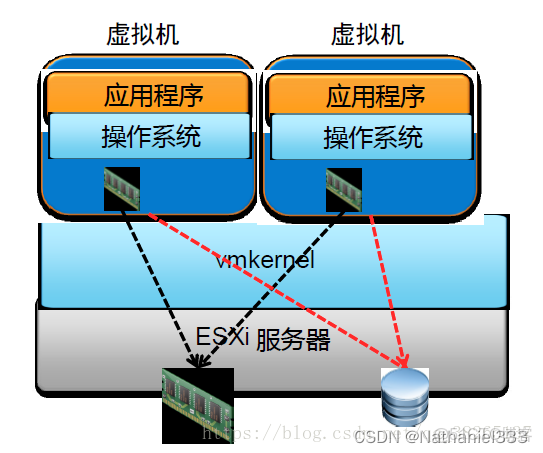

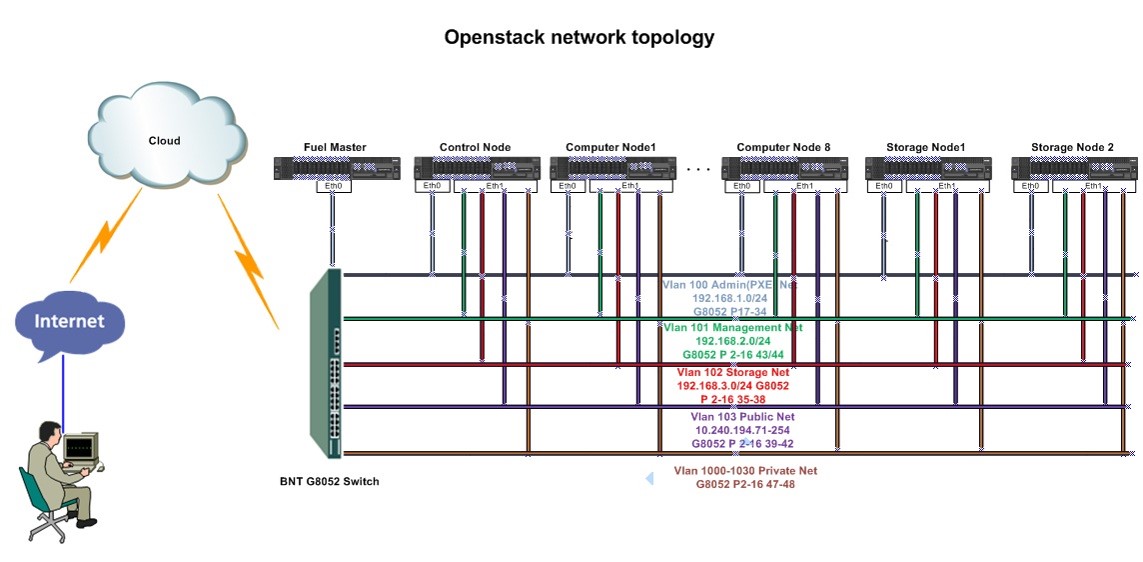

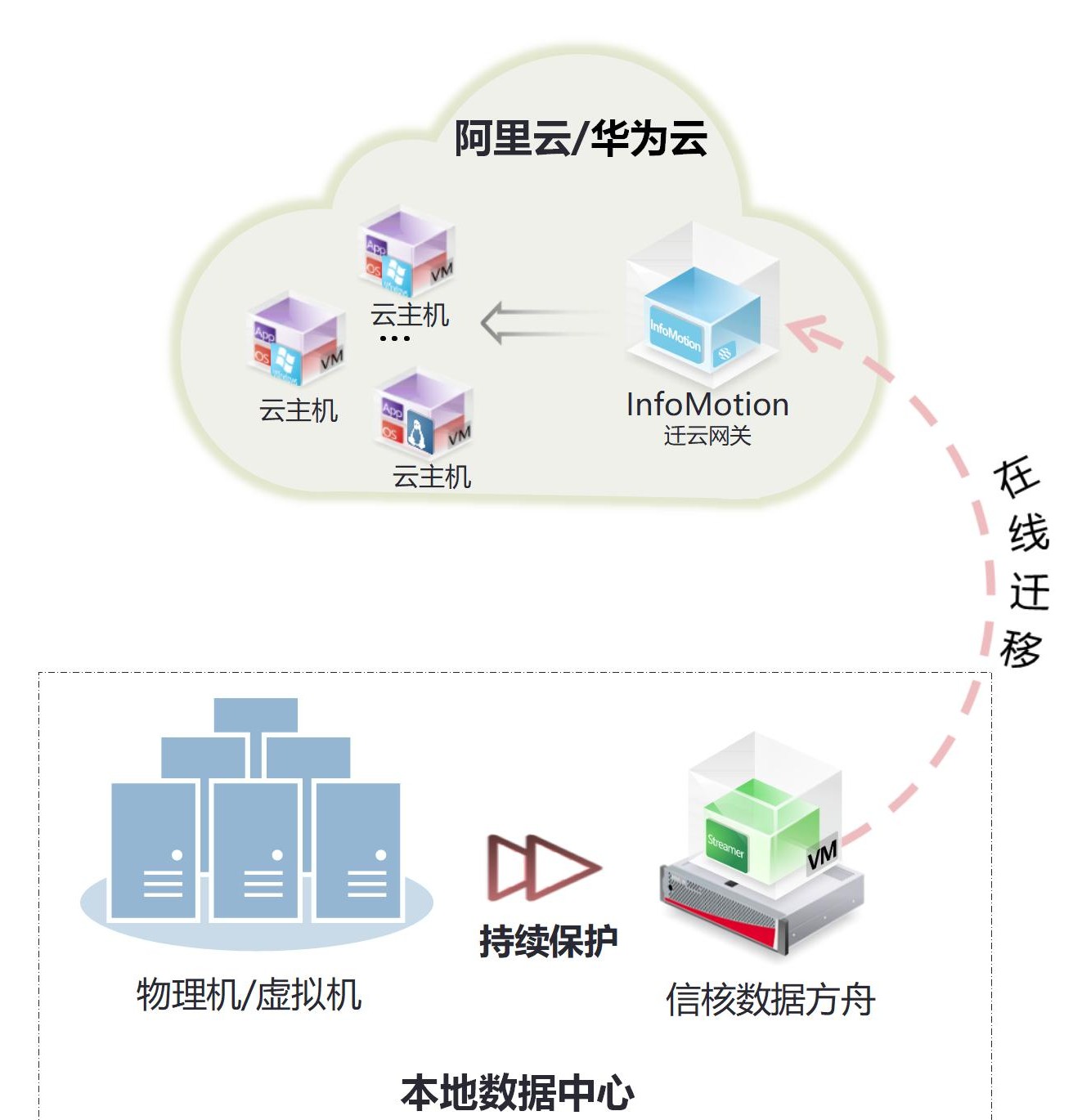

云原生环境

容器技术基于命名空间和cgroups实现轻量化抽象:

️ 核心价值:单台物理主机可承载数百个相互隔离的抽象机实例

资源调度:Kubernetes根据负载动态分配vCPU/内存资源

️ 安全增强:Seccomp过滤系统调用,AppArmor限制权限

演进趋势展望

随着异构计算时代的到来,抽象机与物理机的边界呈现模糊化趋势:

DSA专用加速器:Google TPU针对TensorFlow优化,本质是特定领域抽象机的物化

量子计算接口:Qiskit等框架正在定义量子抽象机编程模型

存算一体架构:新型忆阻器可能重构冯·诺依曼瓶颈,催生新一代抽象机范式

相关问答FAQs

Q1: 为什么说”同一抽象机可以运行在不同物理机上”?

A: 因为抽象机仅规定指令的行为语义,不限定具体实现方式,只要物理机完整实现了该ISA的所有指令,就能正确执行对应的二进制程序,例如Linux内核既能在Intel x86服务器运行,也能在IBM PowerPC小型机启动,正是得益于抽象机的跨平台特性。

Q2: 物理机的哪些改进不会影响抽象机层面的表现?

A: 以下三类改动通常对上层透明:①工艺制程升级(从14nm到7nm);②内部缓存大小调整;③电源管理策略优化,这些属于物理机自身的性能提升,只要保持ISA接口不变,抽象机层面的程序无需修改即可受益,但若修改指令编码格式或寄存器数量