分页存储管理系统物理地址逻辑地址页大小

- 行业动态

- 2025-05-03

- 3

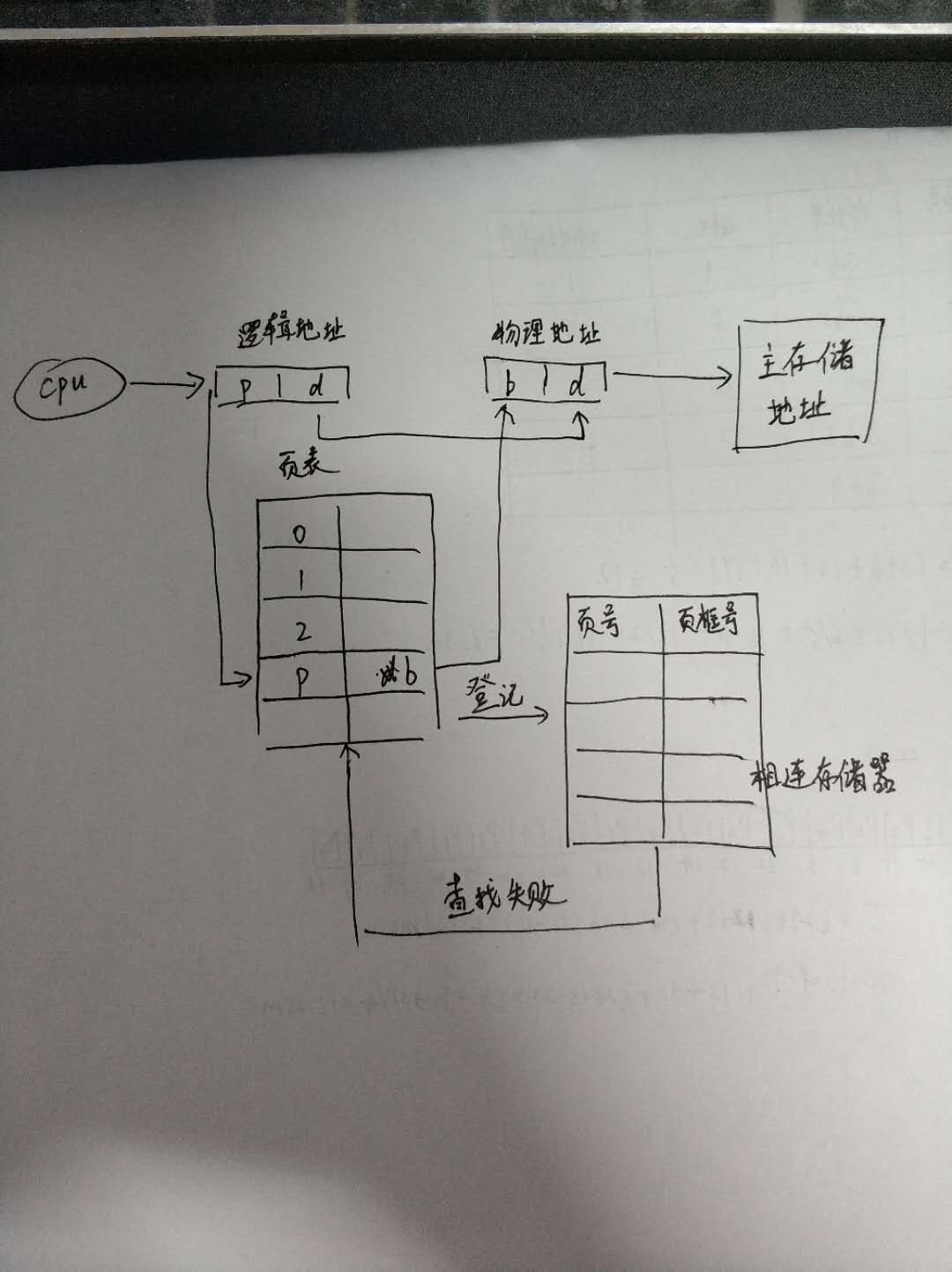

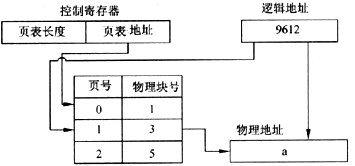

分页系统中,逻辑地址由页号和页内偏移构成,页大小决定偏移位数,物理地址通过页表将逻辑页号映射为物理页框

分页存储管理系统中物理地址、逻辑地址与页大小的深度解析

分页存储管理的核心概念

分页存储管理系统通过将进程的逻辑地址空间划分为固定大小的页(Page),并将物理内存划分为相同大小的页帧(Frame),实现逻辑地址到物理地址的映射,这种机制解决了传统分区存储的外部碎片问题,同时简化了内存分配与回收流程。

核心组件:

- 页表(Page Table):记录逻辑页号到物理页帧号的映射关系

- 页大小(Page Size):决定地址划分粒度的关键参数

- 地址转换机构:完成逻辑地址到物理地址的翻译

逻辑地址与物理地址的结构对比

在分页系统中,地址被划分为两个字段:

| 地址类型 | 结构说明 | 示例(页大小4KB) |

|---|---|---|

| 逻辑地址 | [页号][页内偏移] | 0x00001234 → 页号2,偏移0x234 |

| 物理地址 | [物理帧号][页内偏移] | 帧号5,偏移0x234 → 0x0005234 |

关键特征:

- 页内偏移长度由页大小决定(如4KB页对应12位偏移)

- 页号/帧号位数取决于地址总线宽度(如32位系统,页号占20位)

- 逻辑页号与物理帧号通过页表建立映射关系

页表的工作机制与实现

页表是分页系统的核心数据结构,典型实现方式如下:

| 参数 | 说明 |

|---|---|

| 表项结构 | 物理帧号 + 状态位(有效/无效、读写权限等) |

| 索引方式 | 逻辑页号直接作为偏移量 |

| 内存消耗 | 进程地址空间页数 × 页表项大小(如1024页×4字节=4KB) |

| 快表(TLB) | 硬件缓存最近使用的页表项,降低内存访问次数 |

两级页表示例(64位系统):

- 外页表:包含1024个条目,每个指向内页表

- 内页表:包含1024个页表项,每个对应4KB物理帧

- 逻辑地址:[外页号][内页号][偏移] → 物理地址

页大小的选择与影响

页大小是分页系统的关键设计参数,典型取值包括:

| 页大小 | 适用场景 | 优缺点分析 |

|---|---|---|

| 4KB | 传统操作系统(Windows/Linux) | 平衡内存利用率与管理开销,适合多进程环境 |

| 2MB/4MB | 大页支持(Huge Pages) | 减少页表项数量,降低TLB缺失率,但可能造成内存浪费 |

| 1GB+ | 超级页面(SuperPages) | 用于特殊应用场景(如数据库),需硬件支持 |

技术影响:

- 内存利用率:小页产生更多内部碎片,大页可能浪费未使用空间

- 页表规模:页大小↑ → 页表项数量↓(如1GB地址空间,4KB页需256项,1MB页只需1024/1024=1项)

- TLB命中率:大页减少地址转换频率,但受限于TLB容量(如Intel CPU TLB通常支持64-512条目)

地址转换的完整流程

以32位系统(页大小4KB)为例:

- 逻辑地址分解:0x00403000 → 页号10(0x00403000 / 0x1000),偏移0x3000

- 页表查询:第10号页表项 → 物理帧号5

- 物理地址生成:帧号5 × 4KB + 偏移 → 0x00053000

- TLB优化:硬件缓存最近使用的页表项,直接命中时跳过内存访问

异常处理:

- 缺页中断:当页表项无效时触发,加载缺页到物理内存

- 权限校验:检查页表项的读写/执行权限位

- 越界检查:确保偏移量小于页大小

分页系统的量化分析

通过数学模型可精确计算系统参数:

| 计算公式 | 说明 |

|---|---|

| 页表项数 = 逻辑地址空间 / 页大小 | 如2GB逻辑地址空间,4KB页 → 2^31 / 2^12 = 2^19 = 524,288项 |

| 页内偏移位数 = log₂(页大小) | 4KB页 → 12位偏移 |

| 最大进程数 = 物理内存 / 页大小 | 8GB内存,4KB页 → 2^33 / 2^12 = 2^21 = 2,097,152进程(理论值) |

性能指标对比:

| 指标 | 小页(4KB) | 大页(2MB) |

|---|---|---|

| TLB缺失率 | 高(频繁访问新页) | 低(较少页面切换) |

| 内存管理开销 | 中等(常规页表扫描) | 高(大页可能导致细粒度不足) |

| 内部碎片率 | 较低(页面小) | 较高(可能浪费整页) |

实际应用中的优化策略

- 反向页表:操作系统维护统一页表,解决多进程页表膨胀问题

- 页着色(Page Coloring):将物理帧按颜色分类,优化内存访问局部性

- 混合页尺寸:同时支持多种页大小(如4KB+2MB),兼顾灵活性与性能

- 硬件辅助:MMU(内存管理单元)实现快速地址转换,支持多级页表

典型案例分析

场景:Linux内核的4KB分页实现

- 逻辑地址:32位(高10位页号,低12位偏移)

- 页表结构:三级页表(PMD→PTE→实际物理帧)

- TLB管理:每个CPU核心配备64条目TLB,支持ASID(地址空间标识符)隔离

Windows的超大页面支持

- 默认页大小:4KB(x86架构)/ 8KB(x64架构)

- 大页配置:通过

/3GB开关或VirtualAlloc函数设置2MB页面 - 性能提升:数据库缓冲池使用大页减少TLB抖动

分页系统的局限性与发展

主要挑战:

- 页表存储开销(多级页表增加复杂度)

- 内部碎片累积(平均每个进程浪费半页内存)

- TLB容量瓶颈(限制并发进程数量)

演进方向:

- HW支持的多级页表(x86的CR3寄存器)

- 软件定义的灵活分页(如Intel EPT技术)

- 自适应页尺寸调整(根据工作负载动态选择)

FAQs

Q1:为什么大多数系统选择4KB作为默认页大小?

A1:4KB是历史形成的工程折衷:① 满足多数程序的代码/数据局部性需求;② 使页内偏移正好占用12位(2^12=4096),便于地址计算;③ 在32位系统中平衡页表项数量(如1GB逻辑地址空间仅需256K个页表项);④ 符合早期硬件MMU的设计规范,现代系统虽支持大页,但4KB仍是基础单位。

Q2:分页系统如何处理逻辑地址到物理地址的转换失败?

A2:当发生缺页异常时,操作系统会执行以下步骤:① 保存当前进程上下文;② 根据缺页地址的页号查找对应的虚拟内存区域;③ 如果该页已在交换区,则触发页面置换(如LRU算法选择被淘汰的物理帧);④ 从交换区加载缺页到物理内存;⑤ 更新页表项为有效状态;⑥ 恢复进程上下文并重新执行引发缺页的指令,整个过程涉及磁盘I/O操作,是分页