分页存储系统地址转换过程

- 行业动态

- 2025-05-03

- 1

分页存储系统将逻辑地址拆分为页号和页内偏移,通过页表查找页号对应的物理帧号,再与

分页存储系统地址转换过程详解

分页存储管理是现代操作系统实现内存管理的核心机制之一,其核心目标是将程序的逻辑地址(虚拟地址)映射到物理内存地址,这一过程涉及逻辑地址的拆分、页表查找、多级页表优化以及TLB(快表)缓存加速等环节,以下是分页存储系统地址转换的详细流程与技术细节分析。

逻辑地址与物理地址的结构

逻辑地址(虚拟地址)

- 由程序生成,包含两部分:

- 页号(Page Number):决定逻辑页在页表中的索引。

- 页内偏移量(Offset):决定数据在页内的具体位置。

- 假设页面大小为4KB(2¹²),则偏移量占12位,剩余高位为页号。

- 由程序生成,包含两部分:

物理地址

- 由页框号(Frame Number)和页内偏移量组成。

- 页框号通过页表映射得到,偏移量直接继承逻辑地址的偏移部分。

单级页表的地址转换流程

单级页表是最简单的分页实现方式,适用于小规模内存管理,以下是具体步骤:

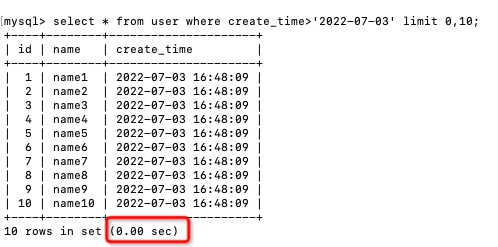

| 步骤 | 操作描述 | 示例(页面大小4KB,逻辑地址0x00BFA004) |

|---|---|---|

| 拆分逻辑地址 | 将逻辑地址分为页号和偏移量。 页号 = 逻辑地址高位,偏移量 = 低位。 | 逻辑地址:0x00BFA004 → 页号=0x00BFA(高位20位),偏移=0x004(低12位)。 |

| 查找页表 | 根据页号查询页表,获取对应的物理页框号。 页表项(PTE)包含物理页框号、有效位、访问权限等。 | 页表[0x00BFA] = 0x12C(假设物理页框号为0x12C,有效位为1)。 |

| 验证有效性 | 检查页表项的有效位(Valid Bit),若无效,触发缺页异常。 | 有效位为1,表示该页已加载到物理内存。 |

| 拼接物理地址 | 物理地址 = 物理页框号 × 页面大小 + 偏移量。 | 物理地址 = 0x12C × 4KB + 0x004 = 0x12C004。 |

多级页表的优化设计

单级页表在64位系统中会导致内存浪费(64位地址空间需要4GB页表),多级页表通过分层索引解决此问题:

多级页表结构

- 外层页表:存储指向内层页表的指针。

- 内层页表:存储实际的物理页框号。

- 示例(二级页表):

- 逻辑地址拆分:页号分为外层页号(Outer Page Number)和内层页号(Inner Page Number)。

- 转换流程:

- 外层页号查找外层页表,得到内层页表的物理地址。

- 内层页号查找内层页表,得到最终物理页框号。

多级页表示例

| 逻辑地址 | 拆分规则 | 转换步骤 |

|————–|—————————-|———————————————————————————-|

| 64位地址 | 外层页号(10位)+ 内层页号(10位)+ 偏移量(12位) | 1. 外层页号查外层页表 → 内层页表地址

内层页号查内层页表 → 物理页框号

拼接物理地址 |

TLB(快表)的作用与原理

TLB的功能

- TLB是页表项的高速缓存,用于加速地址转换。

- 每次内存访问时,优先查询TLB,若命中则直接使用缓存的页框号;若未命中,则访问内存中的页表。

TLB命中率优化

- 硬件实现:TLB通常采用全相联或组相联映射,容量较小(如64-128项)。

- 替换策略:LRU(最近最少使用)或FIFO(先进先出)。

页表项(PTE)的关键字段

页表项不仅存储物理页框号,还包含以下元信息:

| 字段名称 | 功能描述 |

|---|---|

| 有效位(Valid) | 标记该页是否已加载到物理内存(0=无效,1=有效)。 |

| 修改位(Dirty) | 标记该页是否被修改过(用于写时复制和页面置换算法)。 |

| 访问权限 | 包括读(R)、写(W)、执行(X)权限,用于内存保护。 |

| 缓存属性 | 指示该页是否可被缓存(如UC=不可缓存,WT=写穿透)。 |

| 物理页框号 | 实际的物理内存地址,用于拼接物理地址。 |

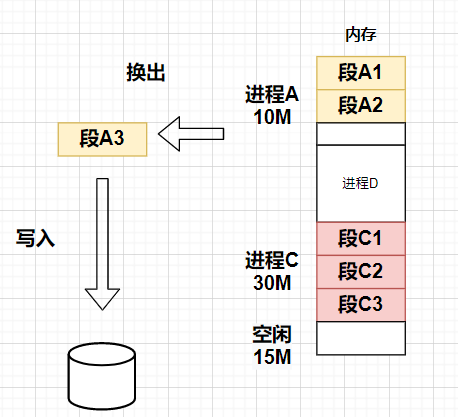

地址转换的例外处理

缺页异常(Page Fault)

- 当页表项的有效位为0时,触发缺页异常。

- 操作系统从磁盘加载对应页面到物理内存,并更新页表。

权限违规

若访问权限不匹配(如写未授权的只读页),触发段错误(Segmentation Fault)。

FAQs

问题1:分页存储系统中,页表的作用是什么?

答:页表是逻辑地址到物理地址的映射表,记录每个逻辑页对应的物理页框号及元信息(如有效位、访问权限),操作系统通过页表实现内存的离散分配和逻辑到物理地址的转换。

问题2:什么是TLB?它如何提高地址转换效率?

答:TLB(Translation Lookaside Buffer)是页表项的高速缓存,用于加速地址转换,TLB缓存近期常用的页表项,避免每次访问内存都查询页表,从而显著降低内存访问延迟,命中率越高,系统性能越接近理想值