上一篇

如何实现存储器的字扩展以提升系统性能?

- 行业动态

- 2025-04-29

- 4052

存储器的字扩展通过增加数据位数扩展存储容量,使用多个同容量芯片并行连接,共享地址线与控制信号,各芯片数据线分别接入系统数据总线不同位,通过地址译码逻辑分配片选信号,实现整体字长增加,满足大位宽数据存储需求。

在计算机系统与嵌入式设备的设计中,存储器扩展是提升数据处理能力的重要手段之一,字扩展(Word Extension)作为存储器扩展的核心方法之一,通过增加存储单元的数据位宽,满足系统对更大数据吞吐量的需求,以下内容将从原理、实现方式、应用场景及注意事项展开,为访客提供全面且专业的解读。

什么是存储器的字扩展?

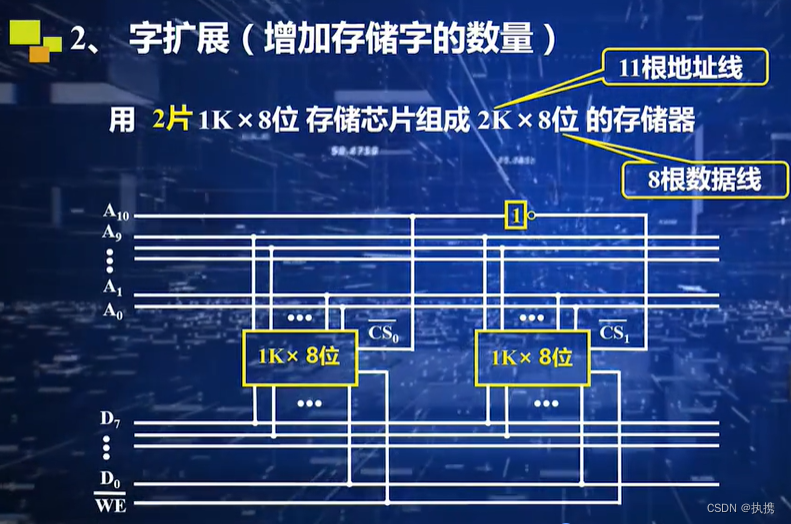

字扩展的目标是扩大存储器的数据位宽,若原有存储器芯片的数据位宽为8位,而系统需要16位的数据处理能力,则可通过字扩展将两片8位芯片并联,形成16位的存储单元,每个地址对应存储的“字长”从8位变为16位,从而适配更高性能的硬件需求。

关键原理

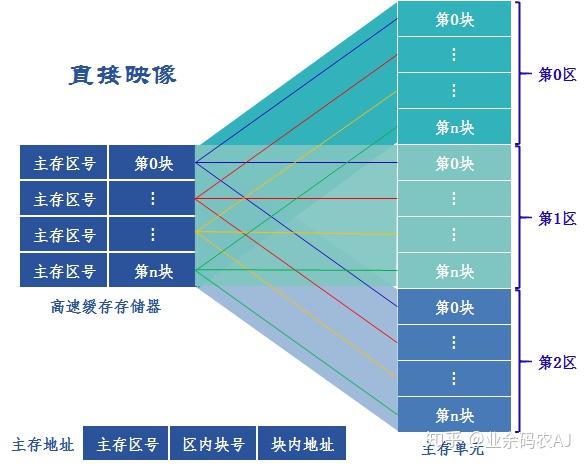

- 位宽叠加:多片存储器芯片的数据线并行连接,总位宽=单芯片位宽×芯片数量。

- 统一寻址:所有芯片共享同一组地址线,由控制信号(如片选信号)协调工作。

字扩展的实现方式

芯片并联法

步骤示例(以8位扩展为16位):

- 选型匹配:选择两片同型号的8位存储器芯片。

- 数据线连接:

- 第一片芯片的数据线连接至系统数据总线的低8位(D0-D7)。

- 第二片芯片的数据线连接至系统数据总线的高8位(D8-D15)。

- 地址线与控制线共享:

- 两片芯片的地址线(A0-An)与系统地址总线直接相连。

- 片选信号(CS)、读/写控制信号(WE/OE)并联,确保同时选中。

特点:

- 成本低,适用于对时序要求不高的场景。

- 需确保芯片的存取速度一致,否则可能引发数据错位。

译码器扩展法

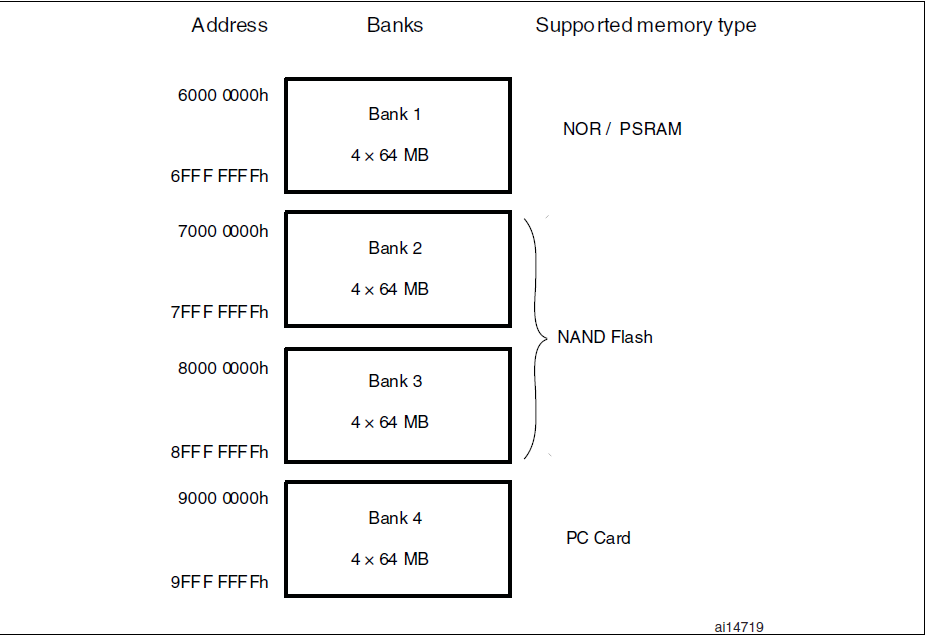

当系统需要同时扩展字长与容量时,可结合译码器实现多组存储芯片的协同工作,使用3-8译码器将地址空间划分为多个区块,每组芯片负责特定区间的数据存储。

实现逻辑:

- 高位地址线(如A15-A13)接入译码器,生成片选信号。

- 低位地址线(A12-A0)直接连接至各芯片,用于片内寻址。

优势:

- 支持更大规模的扩展,灵活性强。

- 需合理规划地址空间,避免冲突。

字扩展的典型应用场景

- 嵌入式系统升级

早期微控制器(如8051)数据总线为8位,通过字扩展兼容16位外设(如LCD模块)。 - 历史硬件维护

修复老式计算机时,若原装存储器停产,可用多片现代芯片替代并扩展位宽。 - 自定义硬件开发

FPGA或ASIC设计中,通过字扩展匹配特定算法的数据位需求。

注意事项与常见问题

电气兼容性

- 电平匹配:不同工艺的芯片可能存在高/低电平差异,需添加电平转换电路。

- 驱动能力:并联芯片可能增加总线负载,需检查主控的驱动能力是否足够。

时序一致性

- 存取时间:若各芯片的读取延迟不同,可能导致数据总线竞争,可通过插入等待周期或选用同批次芯片解决。

散热与功耗

- 多片芯片同时工作可能增加功耗,需评估散热设计是否达标。

地址重叠问题

- 译码器设计不当可能导致多个芯片响应同一地址,引发数据冲突,建议使用逻辑分析仪验证地址映射。

字扩展 vs. 位扩展 vs. 字位扩展

- 字扩展:增加数据位宽(如8位→16位)。

- 位扩展(容量扩展):增加存储单元数量(如1KB→2KB)。

- 字位扩展:同时扩展位宽与容量,需结合译码器与并联技术。

存储器的字扩展是硬件设计中的基础技能,其核心在于通过并联与译码实现数据位宽的灵活扩展,实际应用中需综合考虑芯片参数、时序、功耗等因素,对于高性能系统,建议优先选择集成度高的大位宽存储器芯片,以简化设计并提升可靠性。

参考资料

- 《计算机组成与设计:硬件/软件接口》David A. Patterson, John L. Hennessy

- 《数字电子技术基础》阎石

- Intel 8086微处理器数据手册(存储器接口章节)