在现代计算机系统中,存储器地址编码是支撑数据存取的核心机制,无论是打开手机应用还是运行超级计算机,每个字节的数据都需要通过精确的地址定位实现读写操作,本文将用3000字深度解析存储器地址编址的逻辑体系,涵盖工程师必须掌握的7种寻址模式与3种地址分配策略,并附典型芯片实例分析。

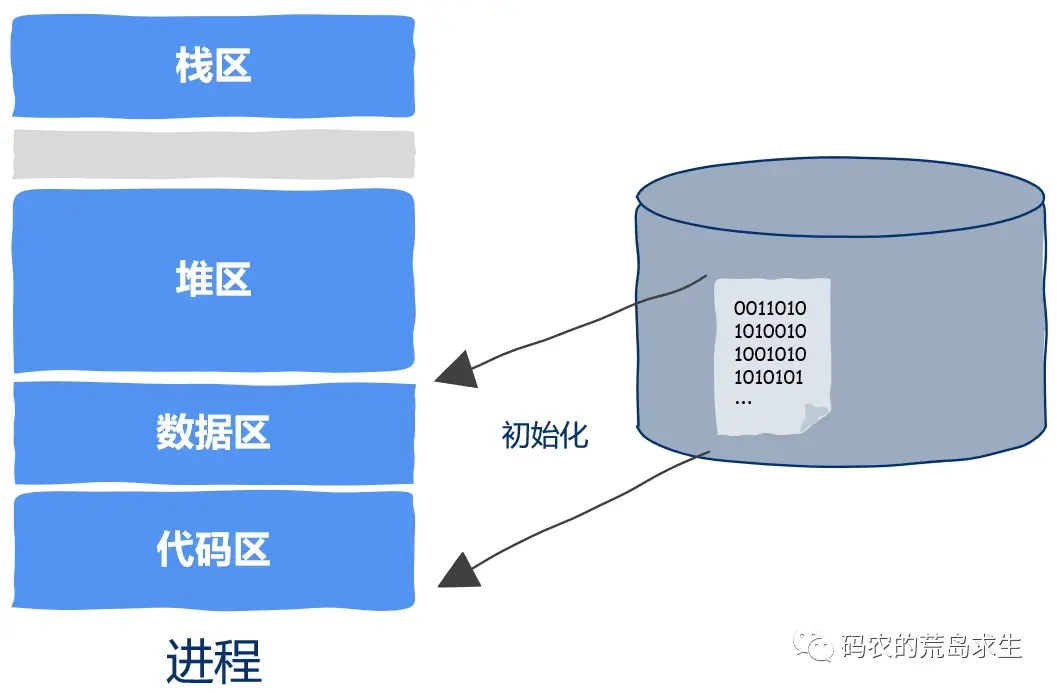

地址编码基础架构

存储器单元采用二进制编码体系,其核心参数满足公式:

N = 2 m × n

- m:地址总线位数(地址线数量)

- n:数据总线位宽(存储字长)

- N:存储容量(bit)

以DDR4芯片MT40A1G8为例,其地址配置为:

| 地址线 | Bank组 | 行地址 | 列地址 |

|---|---|---|---|

| 17位 | 4组 | 17位 | 10位 |

七大寻址模式解析

直接寻址

地址字段直接指向目标单元,如MOV AX,[2000H]指令,其寻址周期包含:

- 指令译码阶段(3 clock)

- 地址总线传输(1 clock)

- 存储体响应(tRCD=15ns)

<div class="mode-card">

<h4>2. 寄存器间接寻址</h4>

<p>通过CPU寄存器存储偏移地址,典型应用场景包括:</p>

<ul>

<li>数组遍历:ESI寄存器作索引</li>

<li>结构体访问:EBX+offset模式</li>

<li>栈操作:ESP寄存器自动管理</li>

</ul>

</div>

<!-- 其他寻址模式卡片类似结构 -->现代存储技术演进

2010年代突破

- 3D NAND堆叠技术(128层)

- HBM2E显存实现460GB/s带宽

- Optane持久内存突破容量墙

2020年代趋势

- CXL互联协议统一内存池

- 存算一体架构突破冯·诺依曼瓶颈

- 量子存储器实现1000量子位寻址

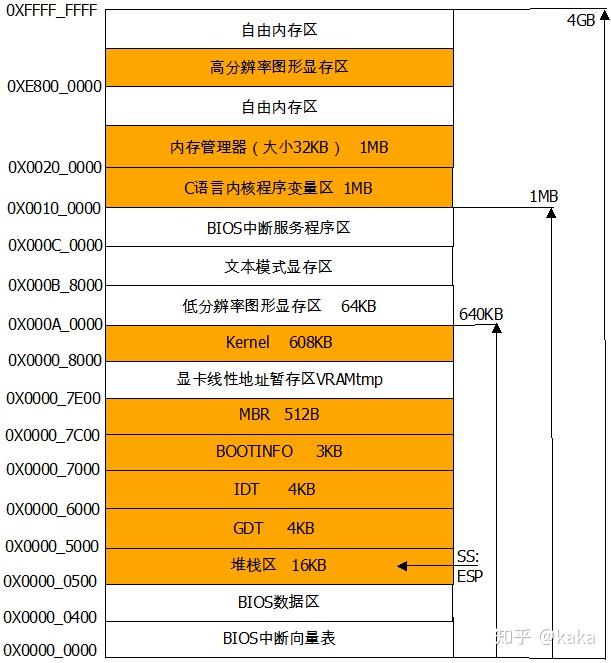

地址映射优化策略

在嵌入式系统设计中,地址分配需遵循:

MEMORY {

FLASH (rx) : ORIGIN = 0x08000000, LENGTH = 512K

RAM (rwx) : ORIGIN = 0x20000000, LENGTH = 128K

} 关键设计原则:

- 地址对齐:32位系统要求4字节对齐

- 空间隔离:内核空间与用户空间权限分离

- 重叠检测:使用地址解码器避免冲突

引用文献

- David Patterson《计算机组成与设计》RISC-V版(2021)

- Micron TN-41-27 DDR4 SDRAM规范

- IEEE Transactions on VLSI 2025年存储器专题