存储器地址线与数据线如何影响你的设备性能?

- 行业动态

- 2025-04-27

- 1

存储器的地址线与数据线:核心功能与设计原理

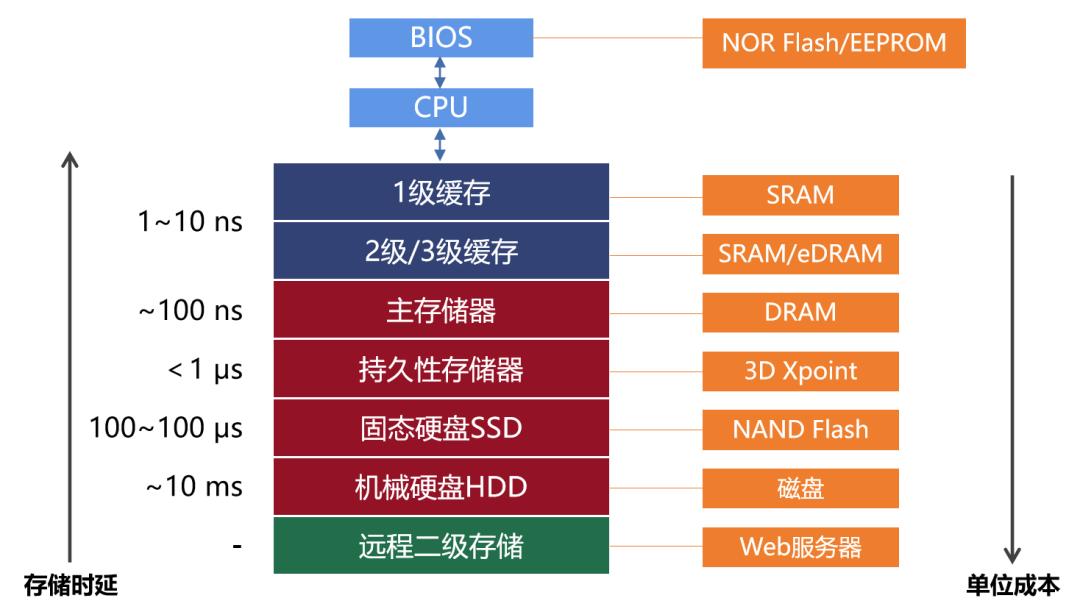

在计算机系统中,存储器(如RAM、ROM)是数据存储与读取的核心部件,地址线和数据线作为存储器的两大关键接口,直接影响存储器的性能与效率,本文将从技术原理、功能差异及实际应用角度,深入解析地址线与数据线的设计逻辑。

地址线:存储单元的“定位器”

功能定义

地址线(Address Bus)用于指定存储器中特定存储单元的位置,当CPU或其他控制器需要访问存储器时,通过地址线发送二进制编码的地址信号,以选中目标单元。决定存储容量

地址线的数量(宽度)决定了存储器可寻址的最大空间。- 10位地址线:支持210=1024个存储单元(1KB)。

- 32位地址线:寻址能力为4GB(232)。

单向传输特性

地址线是单向信号线,仅由控制器(如CPU)向存储器发送地址信息,方向不可逆。

数据线:数据的“搬运通道”

功能定义

数据线(Data Bus)负责在存储器和控制器之间传输实际数据,包括读取(从存储器到CPU)和写入(从CPU到存储器)两种操作。决定数据传输效率

数据线的数量(宽度)直接影响单次传输的数据量:- 8位数据线:每次传输1字节(8 bit)。

- 64位数据线:单次传输8字节,速度提升8倍。

双向传输特性

数据线支持双向传输,根据操作类型(读/写)切换数据传输方向。

地址线与数据线的协同工作

存储器访问流程示例:

- CPU发送地址:通过地址线输出目标存储单元地址(如0x0010)。

- 存储器响应:定位到地址0x0010对应的存储单元。

- 数据操作:

- 写入:CPU通过数据线将数据发送至该单元。

- 读取:存储器通过数据线将数据返回CPU。

时序关系:地址信号需在数据操作前稳定,否则可能导致读写错误。

设计中的关键考量

地址线宽度与存储器扩展

若系统需要扩展存储容量,需增加地址线数量或采用地址复用技术(如DRAM中的行/列地址分时传输)。数据线带宽与性能瓶颈

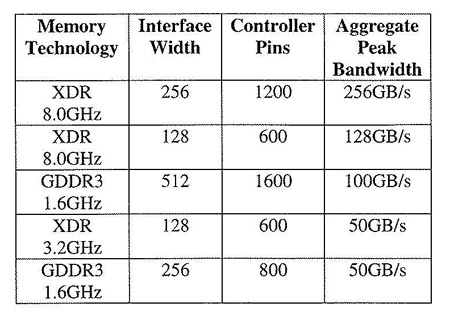

数据线频率(如DDR4的3200MHz)和宽度共同决定总带宽:

带宽 = 数据线宽度 × 频率 ÷ 8

64位数据线@3200MHz的带宽为25.6GB/s(64×3200÷8÷1000)。电磁干扰与信号完整性

高频信号下,地址线和数据线需考虑阻抗匹配、串扰抑制,常用差分信号(如DDR5的DQS信号)增强抗干扰能力。

典型应用场景对比

| 场景 | 地址线作用 | 数据线作用 |

|---|---|---|

| CPU读取指令 | 定位程序代码所在存储单元 | 传输指令代码到CPU |

| GPU显存写入帧数据 | 指定显存中的像素存储位置 | 将渲染后的图像数据写入显存 |

| SSD闪存块擦除 | 选定NAND闪存中的物理块地址 | 传输擦除指令与状态反馈 |

常见问题解答

Q1:地址线和数据线能否复用?

答:部分低功耗设备可能复用引脚以节省成本,但需通过时序控制分时切换功能,会增加设计复杂度。

Q2:为何现代存储器数据线多为64位?

答:64位宽度可匹配CPU字长,单次传输满足多数数据处理需求,兼顾效率与成本。

Q3:地址线数量不足时如何扩展容量?

答:可采用Bank切换(如Flash存储器)或外接地址译码器扩充寻址范围。

引用说明

本文技术参数参考自《计算机组成与设计》(David A. Patterson, John L. Hennessy)及JEDEC固态技术协会公布的DDR4/5标准文档,应用场景案例来源于Intel与AMD公开的处理器架构白皮书。