上一篇

存储器逻辑图如何影响你的硬件设计?

- 行业动态

- 2025-04-26

- 3824

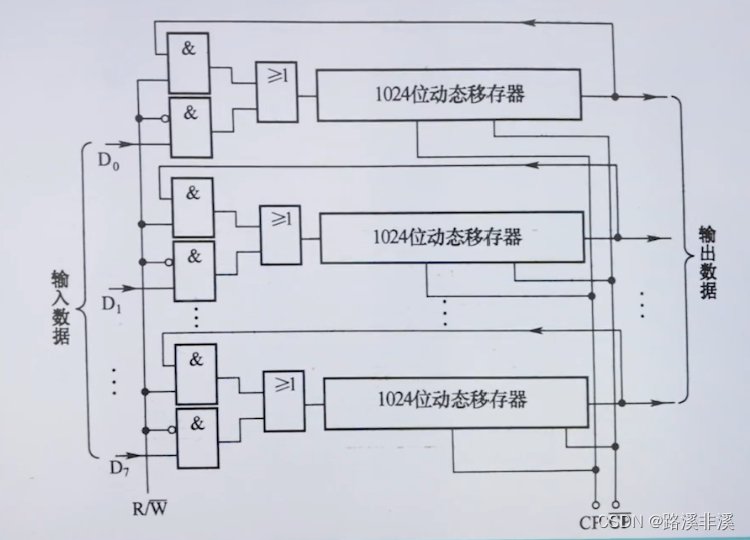

存储器逻辑图展示了存储单元阵列、地址译码器、读写控制电路及数据缓冲器的连接关系,地址译码器通过地址线选中特定存储单元,读写控制电路根据指令管理数据存取,数据缓冲器协调内外传输速度差异,共同实现数据的存储与调用,其结构直观反映了存储系统的核心工作原理。

核心原理与设计要点

存储器是计算机系统的核心组件之一,其逻辑图描述了内部结构和工作原理,本文通过拆解存储器的逻辑图,帮助读者理解其设计逻辑、模块功能及实际应用。

存储器逻辑图的定义与作用

存储器逻辑图是一种图形化表示方式,展示了存储器内部各功能模块的连接关系和数据流动路径,通过逻辑图,可以直观了解存储器的以下特性:

- 数据存储结构:如何通过地址线、数据线实现数据的读写。

- 控制信号交互:读写信号(Read/Write)、片选信号(Chip Select)等如何协调工作。

- 容量与位宽:地址总线和数据总线的位数如何决定存储器的容量和传输效率。

逻辑图不仅是硬件设计的基础,也是故障诊断和性能优化的关键工具。

存储器逻辑图的基本组成模块

典型的存储器逻辑图包含以下核心模块:

地址译码器(Address Decoder)

- 功能:将输入的二进制地址转换为对应的行/列选择信号,定位到特定存储单元。

- 设计要点:译码器的复杂度与地址位数相关(如N位地址对应2^N个存储单元)。

存储单元阵列(Memory Cell Array)

- 结构:由行列交叉的存储单元构成,每个单元存储1位数据(0或1)。

- 类型:静态随机存储器(SRAM)单元由触发器构成;动态随机存储器(DRAM)单元由电容和晶体管构成。

读写控制电路(Read/Write Control Circuit)

- 功能:根据控制信号(Read/Write)切换数据流动方向。

- 关键技术:时序控制(如DRAM的预充电、刷新周期)。

数据输入/输出缓冲器(I/O Buffer)

- 作用:临时存储输入或输出的数据,提高与外部总线的兼容性。

(示例图:地址译码器→存储单元阵列→读写控制电路→I/O缓冲器)

存储器逻辑图的工作原理

以下以“读取数据”为例,说明逻辑图的运行流程:

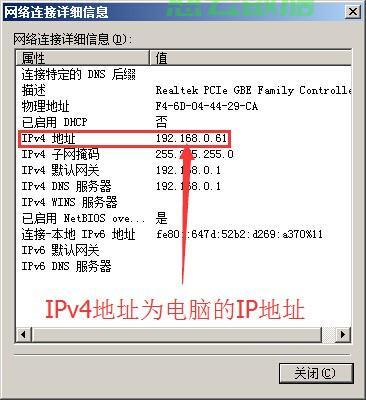

- 地址输入:CPU通过地址总线发送目标地址(如8位地址“00001111”)。

- 地址译码:译码器将地址转换为行/列选择信号,选中对应存储单元。

- 数据读取:读写控制电路激活“读”信号,存储单元中的数据经位线传输至I/O缓冲器。

- 数据输出:缓冲器将数据推送至数据总线,完成读取操作。

写入操作的流程类似,区别在于控制信号为“写”,数据从总线经缓冲器写入存储单元。

常见存储器类型及其逻辑图差异

静态存储器(SRAM)

- 特点:逻辑图中包含触发器电路,无需刷新,读写速度快但成本高。

- 应用场景:CPU高速缓存(Cache)。

动态存储器(DRAM)

- 特点:逻辑图包含电容刷新电路,结构简单、密度高,但需要周期性刷新。

- 应用场景:计算机主内存(RAM)。

只读存储器(ROM)

- 特点:逻辑图中无写入电路,数据固化在制造阶段(如掩膜ROM)。

- 变种:可编程ROM(PROM)、闪存(Flash)等支持有限次写入。

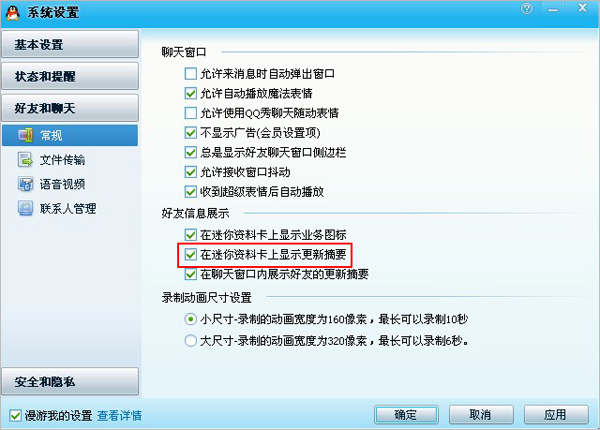

存储器逻辑图设计的关键考量

- 功耗优化:动态存储器的刷新电路设计影响整体功耗。

- 时序匹配:读写信号与地址/数据的传输必须严格同步。

- 抗干扰能力:通过冗余校验位(如ECC)提升数据可靠性。

- 扩展性:通过片选信号实现多存储器芯片的级联。

实际案例分析:DDR4内存逻辑图简化解读

以DDR4内存为例,其逻辑图包含以下高级模块:

- 双数据率(DDR)接口:在时钟上升沿和下降沿均传输数据,提升带宽。

- Bank分组结构:将存储阵列分为多个Bank,支持并行操作。

- 模式寄存器(Mode Register):存储时序参数(如CL值),供控制器调用。

引用说明

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- 英特尔《DDR4 SDRAM技术白皮书》

- IEEE论文《Memory Architecture Optimization for Low-Power Systems》