上一篇

存储器片内地址如何影响数据存取效率?

- 行业动态

- 2025-04-29

- 1

存储器片内地址指芯片内部用于定位存储单元的二进制编码,由地址线数量决定寻址范围,每个地址对应唯一存储单元,通过地址总线输入后经译码电路选中目标位置,片内地址需配合片选信号共同作用,实现多芯片系统中的精确访问,地址位数直接影响芯片容量,例如10位地址可寻址1024个单元。

存储器片内地址详解

在计算机系统和电子设备中,存储器是存储和读取数据的关键组件,存储器的性能与设计直接影响设备的速度、效率和可靠性,而存储器片内地址(On-Chip Memory Address)作为存储器的核心概念之一,决定了数据如何被精准定位和管理,以下从多个维度深入解析这一技术概念。

存储器片内地址的基本概念

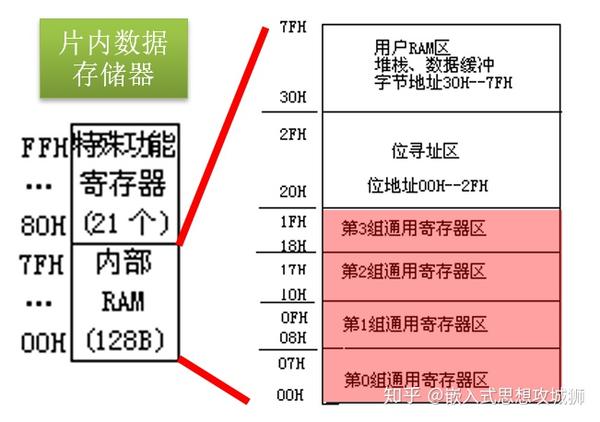

存储器片内地址是指存储芯片内部用于标识存储单元的唯一编号,每个存储单元对应一个地址,通过地址总线传输的二进制编码可以访问特定单元中的数据,一个容量为1KB的存储器芯片,其片内地址范围为0x000到0x3FF(十六进制)。

关键点:

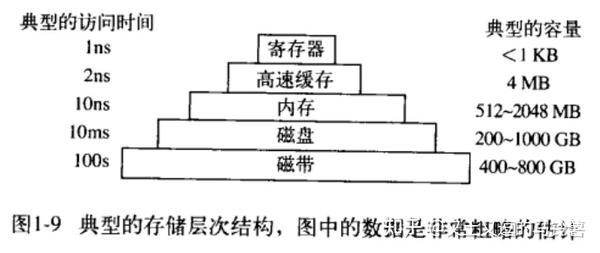

- 地址线与存储容量的关系:地址线的数量直接决定存储器容量,若芯片有 n 根地址线,可寻址的单元数为 (2^n),10根地址线支持 (2^{10}=1024) 个单元(即1KB)。

- 地址译码器:将输入的二进制地址转换为物理存储单元的选通信号,确保数据准确读写。

片内地址的结构与组成

存储器的片内地址通常由以下模块构成:

地址总线(Address Bus)

- 负责将CPU或其他控制器生成的地址传输至存储器芯片。

- 总线宽度与地址线数量一致,例如32位总线支持 (2^{32})(约4GB)的寻址空间。

地址译码电路

- 分为行译码器和列译码器,用于定位存储单元的行列坐标(如DRAM)。

- 一个16×16的存储阵列,4位地址可解析行地址,剩余4位解析列地址。

存储单元阵列

由晶体管和电容组成的矩阵结构,每个单元存储1位数据。

示例代码:简单地址译码逻辑

module address_decoder(input [3:0] addr, output reg [15:0] select);

always @(*) begin

case(addr)

4'b0000: select = 16'b0000000000000001;

4'b0001: select = 16'b0000000000000010;

// ... 其他地址译码

endcase

end

endmodule 片内地址的寻址方式

根据存储器类型的不同,片内地址的寻址方式可分为以下几类:

| 寻址方式 | 特点 | 应用场景 |

|---|---|---|

| 线性寻址 | 地址连续递增,无复用结构 | SRAM、寄存器文件 |

| 行列复用寻址 | 地址分拆为行和列,减少地址线数量 | DRAM、Flash存储器 |

| 分块寻址 | 将存储空间划分为多个块,按块访问 | 高速缓存(Cache) |

典型场景分析:DRAM的地址复用

- 行地址选通(RAS)与列地址选通(CAS)分时复用同一组地址线,降低引脚数量。

- 1Gb DRAM芯片通过10位地址线分两次传输行和列地址(共20位),支持 (2^{20}) 个单元。

片内地址的实际应用与优化

嵌入式系统设计

- 在单片机中,片内SRAM的地址直接映射到CPU的寻址空间,实现高速数据访问。

- 优化策略:通过地址对齐(Alignment)提高总线传输效率。

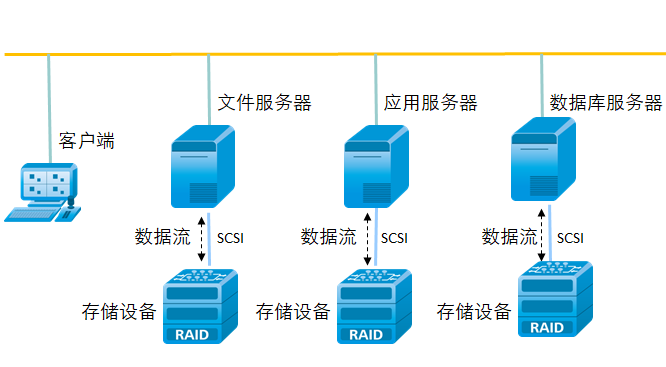

存储器扩展技术

- 地址空间重叠:通过片选信号(Chip Select)扩展多片存储器。

- 示例:若系统需要4片1KB存储器,可通过2位片选信号+10位片内地址实现4KB总容量。

低功耗设计

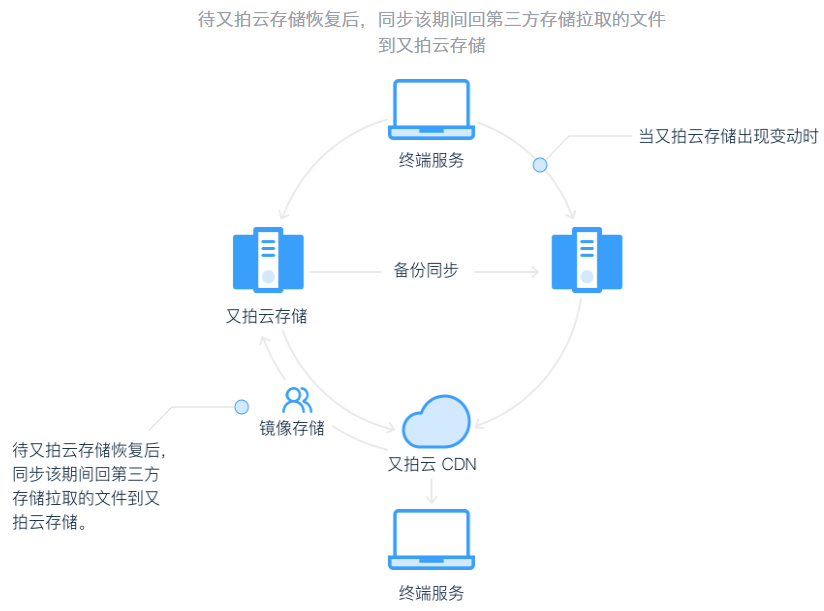

- 地址分区休眠:关闭未访问区域的电源,减少静态功耗。

常见问题解答

为什么存储器容量通常是2的幂次?

地址线数量为整数,存储单元数自然为 (2^n),3根地址线对应8个单元((2^3=8))。

片内地址与片外地址有何区别?

片内地址指向芯片内部的存储单元,而片外地址用于选择不同的存储芯片(通过片选信号)。

地址线数量不足时如何扩展容量?

- 采用分页技术或多级译码,将地址分批次传输。

引用说明

- [1] 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- [2] IEEE标准《半导体存储器测试方法》(IEEE 1521-2004)

- [3] 三星电子《DRAM技术白皮书》(2022版)