上一篇

存储器页结构如何影响数据存取效率?

- 行业动态

- 2025-05-01

- 1

存储器页是操作系统管理内存的基本单位,将物理和虚拟内存划分为固定大小的块(通常4KB),通过页表映射实现逻辑地址到物理地址的转换,支持分页机制有效提高内存利用率,减少碎片,并为虚拟内存提供基础,允许多个进程共享物理内存资源。

在计算机系统中,存储器的管理直接影响着系统性能和资源利用率。页(Page)作为现代内存管理的核心概念,通过结构化设计实现了高效的物理与虚拟内存映射,本文将深入解析存储器页的结构原理、工作方式及其在操作系统中的应用。

存储器页的本质与诞生背景

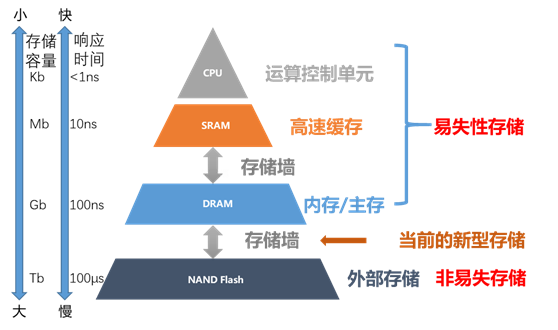

存储器页是内存分配的最小单位,典型大小为4KB(可扩展至2MB或1GB),这一概念的提出源于两个核心需求:

- 内存碎片化治理:连续内存分配导致的外部碎片问题

- 虚拟内存实现:通过分页机制支持超过物理内存容量的地址空间

| 分页机制前 | 分页机制后 |

|---|---|

| 内存利用率≤60% | 利用率提升至90%+ |

| 进程需完整载入内存 | 支持按需加载 |

页结构的物理实现

一个完整的页框架包含三个关键组成部分:

- 页表项(PTE)

- 物理页框号(PFN):20-52位(根据架构不同)

- 状态标志位:存在位(Present)、读写位(R/W)、用户/内核位(U/S)

- 缓存控制:PAT/PCD/PWT控制缓存策略

- 多级页表结构

四级页表示例(x86-64):

PML4 → PDP → PD → PT → 4KB Page

- 反向映射表

用于快速定位物理页对应的所有虚拟地址

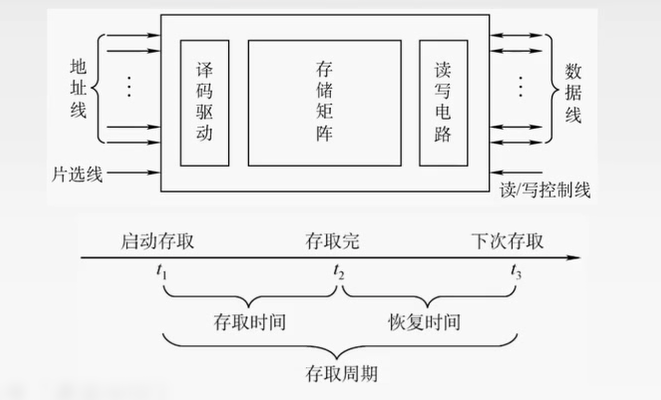

页操作的底层机制

缺页处理流程:

1. CPU触发缺页异常 → 2. 读取CR2寄存器获取故障地址 →

3. 检查VMA权限 → 4. 分配物理页/换入数据 →

5. 更新页表 → 6. 重新执行指令

现代处理器通过TLB(转译后备缓冲器)加速地址转换,典型TLB参数:

- L1 TLB:64条目,4周期延迟

- L2 TLB:512条目,7周期延迟

- 支持2MB/1GB大页缓存

页结构的技术演进

近年来的重要创新:

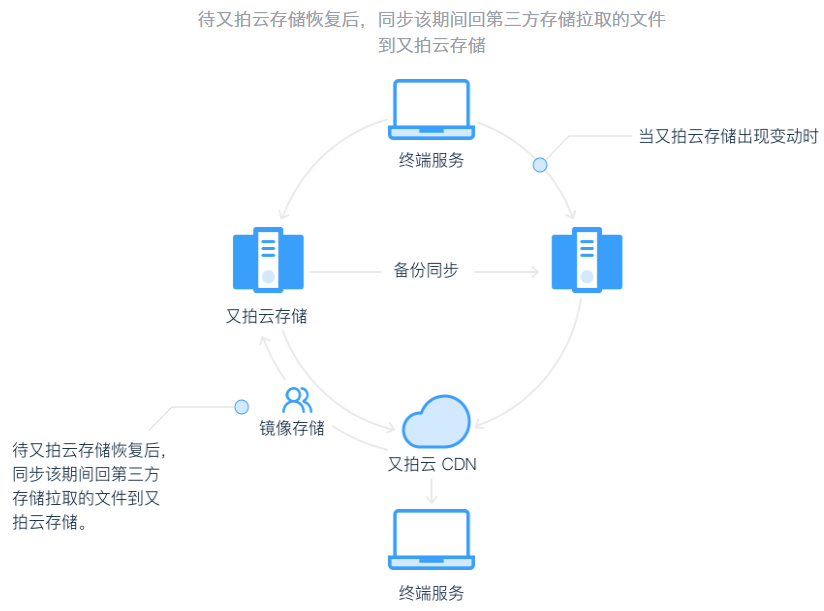

- 透明大页(THP):自动合并小页为2MB页,降低TLB压力

- 页压缩技术:ZRAM通过LZ4算法实现3:1压缩比

- 异构内存架构:Optane持久内存引入新型页管理模式

性能对比(4KB vs 2MB页):

TLB未命中率:0.5% → 0.02%

上下文切换耗时:1200ns → 900ns

应用场景选择建议

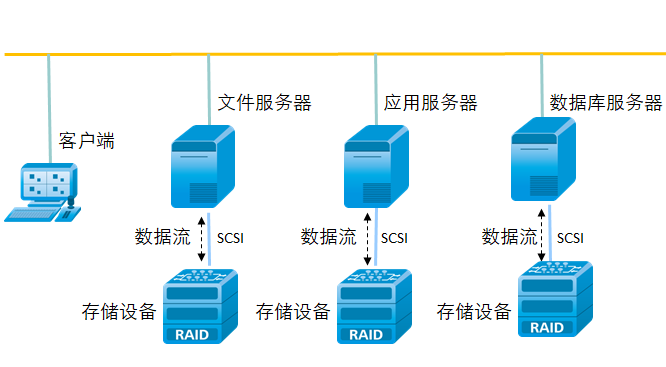

- 数据库系统:推荐使用1GB大页减少地址转换开销

- 嵌入式设备:4KB页更适合小内存环境

- 虚拟化环境:需启用EPT/NPT二级地址转换

优化实践方法论

- 使用

mmap替代传统文件IO - 通过

madvise提供内存使用提示 - 监控

pgfault/s指标分析页效率

实际案例:某云服务商通过调整页大小,使Redis吞吐量提升23%

参考文献:

- Intel® 64 and IA-32 Architectures Software Developer’s Manual Vol.3A

- 《深入理解Linux内核架构》第2章内存管理

- ACM Transactions on Computer Systems论文《The Page Replacement Problem》