存储器扩展地址如何影响系统性能与升级方案?

- 行业动态

- 2025-04-28

- 3

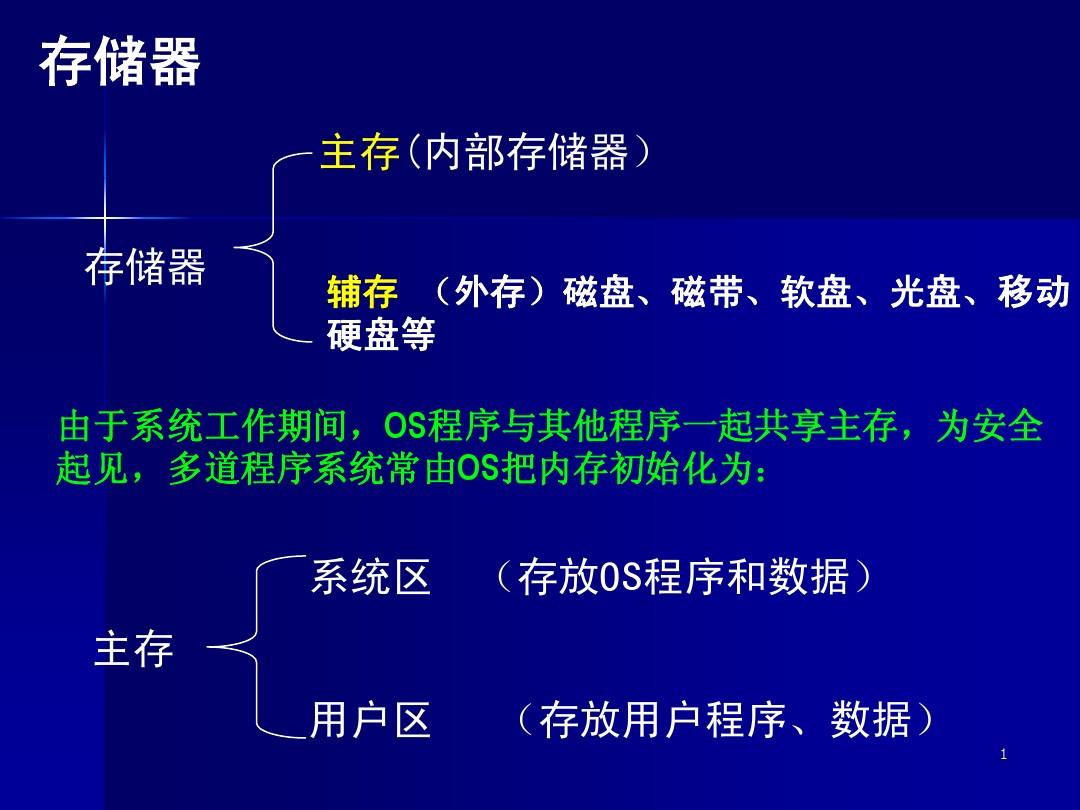

存储器扩展地址是指通过地址总线扩展或分页技术突破主存容量限制的方法,常用于计算机系统和嵌入式设备中,通过连接多块存储芯片或采用地址译码技术,扩展物理寻址空间,提升存储容量与系统性能,满足复杂应用需求。

在计算机系统、嵌入式设备及各类电子设备的设计中,存储器扩展地址是一个关键概念,它决定了如何通过有限的硬件资源满足更大的存储需求,无论是开发人员、硬件工程师,还是对计算机原理感兴趣的爱好者,理解存储器扩展地址的原理与实践都至关重要,本文将深入解析其核心概念、实现方式及实际应用场景。

什么是存储器扩展地址?

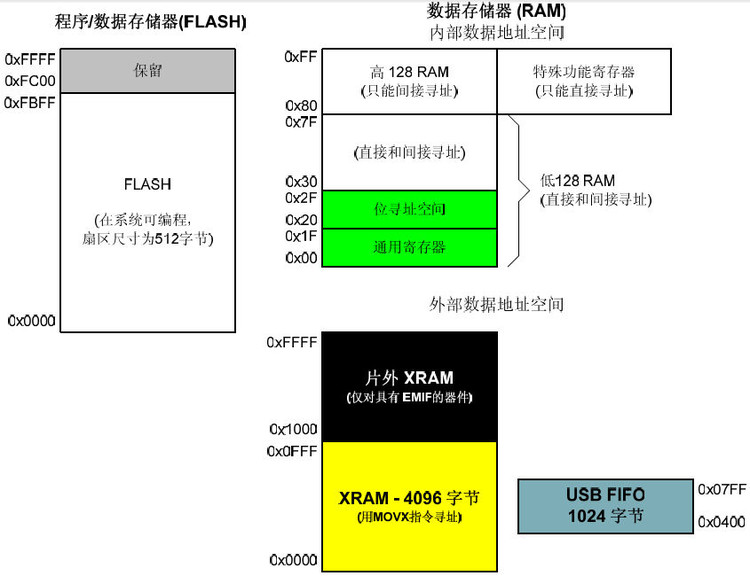

存储器扩展地址(Memory Address Extension)是指通过特定的硬件或软件技术,扩展系统可访问的存储空间范围,在计算机体系结构中,处理器的地址总线宽度决定了其可直接寻址的存储容量,一个16位地址总线的系统最多支持64KB(2^16)的寻址空间,如果实际需求超过这一限制,就需要通过扩展地址的方式突破瓶颈。

核心作用:

- 突破硬件限制:弥补处理器地址总线宽度不足的问题。

- 支持大容量存储:满足现代应用对海量数据存储的需求(如数据库、图像处理)。

- 灵活管理资源:通过分块或分段机制实现多任务环境下的内存分配。

存储器扩展的实现方式

位扩展(Bit Extension)

位扩展通过增加存储器的数据位宽(即每个存储单元存储的位数)来提升存储容量,将8位的数据总线与两块8位存储器并联,实现16位数据输出。

- 实现关键:

- 使用片选信号(Chip Select, CS)控制多块存储芯片的协同工作。

- 地址线直接连接到所有存储芯片的地址端口。

字扩展(Word Extension)

字扩展通过增加存储单元的数量来扩大寻址范围,使用译码器将地址空间分割为多个块,每块对应一个存储芯片。

- 实现关键:

- 地址译码器:将高位地址线输入译码器,生成片选信号。

- 分块管理:每个存储芯片负责特定地址区间的数据存储。

混合扩展(Bit-Word Extension)

结合位扩展与字扩展,同时增加数据位宽和存储单元数量,实现更大容量的存储器系统。

- 典型场景:

构建32位数据总线系统时,使用4块8位存储芯片进行位扩展,再通过译码器扩展存储单元数量。

地址分配与译码

地址线分配原则

- 低位地址线:直接连接存储芯片,用于选择芯片内的存储单元。

- 高位地址线:输入译码器,生成片选信号以选择具体的存储芯片。

示例:

假设系统地址总线为20位(可寻址1MB空间),使用8块128KB的存储芯片:

- 低位17位地址线(A0-A16)用于选择每个芯片内的128KB空间(2^17 = 131072 = 128KB)。

- 高位3位地址线(A17-A19)输入3-8译码器,生成8个片选信号。

常用译码器类型

- 简单门电路译码:适用于小规模扩展(如2-4译码器)。

- 专用译码芯片:如74HC138(3-8译码器)、74HC154(4-16译码器)。

- 可编程逻辑器件(PLD):提供灵活的译码逻辑设计,适合复杂系统。

应用场景与挑战

典型应用

- 嵌入式系统:在资源受限的微控制器(如8051、ARM Cortex-M)中扩展外部RAM或Flash。

- 服务器内存扩展:通过多通道内存技术支持TB级数据存储。

- 工业控制设备:管理大规模传感器数据与历史记录。

常见问题与解决方案

- 地址冲突:确保译码逻辑的唯一性,避免多个芯片响应同一地址。

- 译码延迟:选择高速译码器以匹配处理器时序。

- 功耗管理:使用低功耗模式或动态关闭未使用的存储模块。

未来趋势

随着存储技术的发展,存储器扩展技术也在不断演进:

- 片上存储器扩展:通过3D堆叠技术(如HBM)在芯片内部集成更大容量存储。

- 虚拟内存技术:结合操作系统实现逻辑地址到物理地址的动态映射。

- 非易失性存储器:利用新型存储介质(如MRAM、ReRAM)突破传统容量与速度限制。

引用说明

本文参考了以下权威资料:

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- Intel® 64 and IA-32 Architectures Software Developer Manuals

- ARM Cortex-M系列技术手册