存储时序如何影响你的计算机性能?

- 行业动态

- 2025-04-29

- 2437

在计算机和电子设备中,存储器(如DRAM、SRAM、闪存等)的性能直接影响系统的整体效率。存储时序作为存储器工作的核心参数,决定了数据读写的准确性和速度,本文将从工作原理、关键参数、影响因素及优化方法等角度,深入解析存储时序的技术细节。

存储时序的核心概念

存储时序(Memory Timing)是指存储器在响应控制器指令时,各操作步骤之间的时间关系,它通过一系列时间参数定义,确保数据在正确的时间窗口内被读取或写入,当CPU向内存发送读取请求时,存储器需经历地址传输→行激活→列选通→数据传输等多个步骤,每一步都需精确的时间配合。

类比理解:想象快递员送货,存储时序类似快递流程中的“分拣→装车→运输→送达”,每个环节耗时不同,但必须严格按顺序和时间间隔完成,否则包裹(数据)可能丢失或延迟。

存储时序的关键参数

存储时序通常由以下核心参数组成(以DDR内存为例):

CL(CAS Latency):列地址选通延迟

从发出列地址到数据输出的时间,单位为时钟周期,CL值越低,数据响应越快,DDR4内存的CL值常见为14-18。tRCD(RAS to CAS Delay):行地址到列地址的延迟

行激活后,需等待tRCD时间才能发送列地址,若tRCD过短,可能导致数据错误。tRP(RAS Precharge Time):行预充电时间

关闭当前行并准备打开新一行所需的时间,影响内存切换效率。tRAS(Row Active Time):行激活周期

一行被激活后,必须保持开启的最短时间,过短的tRAS会导致频繁刷新,增加延迟。Command Rate:命令速率

内存控制器发送指令的间隔时间,通常为1T或2T(T为时钟周期),高频率内存可能需放宽此参数以提高稳定性。

时序示例:DDR4-3200的典型时序为CL16-18-18-36,分别对应CL、tRCD、tRP、tRAS的值。

影响存储时序的因素

硬件设计

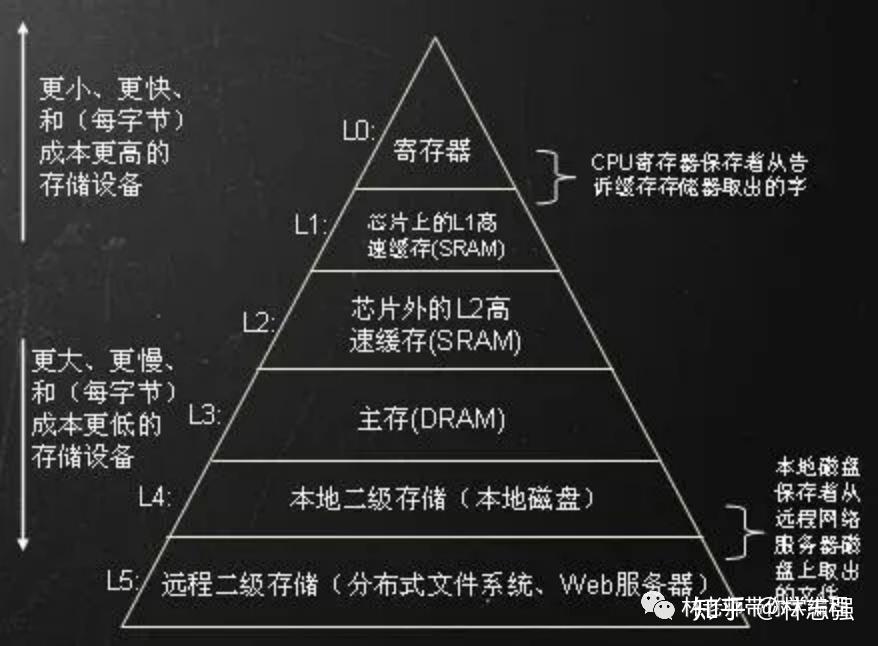

- 存储器类型:SRAM无需刷新,时序简单;DRAM需定期刷新,时序更复杂。

- 工艺制程:先进工艺(如10nm以下)可缩短晶体管响应时间,降低延迟。

工作频率与电压

- 频率提升会缩短时钟周期,但时序参数可能需放宽以保持稳定。

- 提高电压可加速晶体管开关速度,但会增加功耗和发热。

控制器与总线设计

内存控制器的调度算法、总线的信号完整性(如PCB走线长度)均会影响时序精度。

存储时序的优化方法

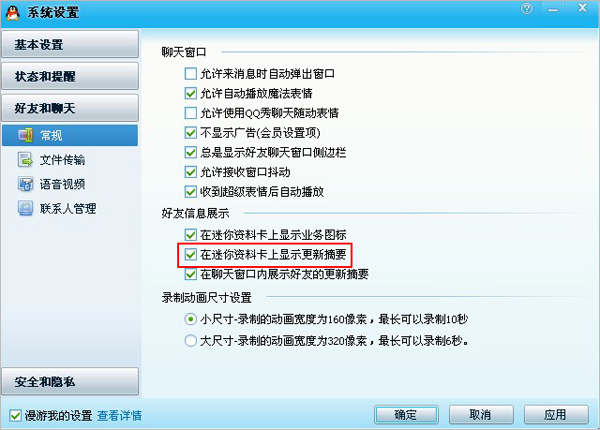

时序调优(手动超频)

在BIOS中调整CL、tRCD等参数,降低延迟,需逐步测试稳定性(如使用MemTest86)。提升信号质量

- 优化PCB布线,减少信号反射和串扰。

- 使用阻抗匹配技术,确保信号传输完整性。

采用先进技术

- DDR5的改进:通过双通道32位子库设计,减少行激活冲突,降低tRCD和tRP。

- GDDR6的PAM4编码:每个周期传输更多数据,间接缓解时序压力。

实际应用中的时序权衡

- 消费级设备:优先平衡性能与成本,游戏PC可能选择CL16 DDR4-3600内存,而办公电脑使用CL22 DDR4-2666。

- 服务器与数据中心:强调稳定性和容量,通常采用ECC内存并放宽时序参数(如CL值增加20%)。

- 嵌入式系统:针对特定负载优化时序,如实时控制系统需严格确保最大延迟上限。

常见误区与解答

误区1:时序越低越好?

并非绝对,若频率提升幅度远超时序增加的影响(如DDR4-4000 CL18对比DDR4-3200 CL16),整体带宽可能更高。

误区2:所有存储器都需手动调时序?

NOR闪存、EEPROM等非易失存储器的时序由物理特性固定,不可调整。

存储时序是存储器性能的“隐形指挥家”,其参数配置需权衡速度、稳定性与功耗,随着3D堆叠、HBM(高带宽内存)等技术的发展,时序管理将面临更复杂的挑战,但核心目标始终不变:在正确的时间,传递正确的数据。

参考文献

- JEDEC固态技术协会. DDR4 SDRAM标准(JESD79-4B). 2017.

- David A. Patterson, John L. Hennessy. 《计算机组成与设计:硬件/软件接口》. 机械工业出版社, 2020.

- Micron Technology. TN-41-01: DRAM Timing Parameters. 2022.