上一篇

如何正确连接存储器地址线?

- 行业动态

- 2025-04-27

- 2348

存储器地址线由CPU或控制器发出,需按顺序对应连接至存储芯片的地址引脚,确保地址信号正确传输,需根据地址总线位数确定连接范围,高位地址可能用于片选控制,低位直接接入芯片,注意电平匹配与信号完整性,避免错位或交叉。

存储器地址线连接方法详解

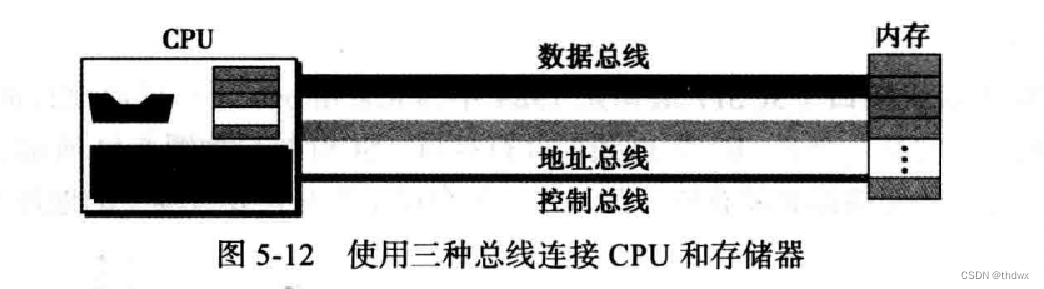

在计算机系统或嵌入式设备中,存储器地址线的正确连接是确保数据读写可靠性的关键一步,地址线的作用是传输CPU或控制器对存储单元的寻址信号,连接错误可能导致系统无法启动、数据丢失或硬件损坏,以下是存储器地址线连接的详细方法与注意事项:

地址线的基本概念

存储器地址线(Address Lines)是一组由CPU或控制器发出的二进制信号线,用于指定存储单元的位置,每根地址线代表一个二进制位,地址线数量(N)决定了可寻址的存储空间大小(20根地址线可寻址1MB空间,即 (2^{20}=1,048,576) 个地址)。

地址线连接的核心步骤

步骤1:确定地址线数量

- 根据存储器芯片的容量,查看其地址线需求。

- 64KB的SRAM需要16根地址线((2^{16}=65,536))。

- 1MB的Flash需要20根地址线。

- 注意:若系统地址线多于存储器需求,需通过高位地址线进行片选(Chip Select)。

步骤2:连接至CPU/控制器

- 直接连接:将存储器的地址引脚(A0~An)与CPU的对应地址线(ADDR0~ADDRn)一一对应连接。

存储器的A0接CPU的ADDR0,A1接ADDR1,依此类推。

- 复用连接:若CPU地址线复用(如数据线与地址线复用),需通过锁存器分离信号(如使用74HC573锁存低8位地址)。

步骤3:电平匹配与驱动能力

- 确认双方接口电平一致(如3.3V或5V),若不一致,需通过电平转换芯片(如TXB0108)适配。

- 检查CPU的驱动能力是否足够驱动存储器地址线负载,必要时增加缓冲器(如74LCX245)。

步骤4:地址线布局与走线

- 布线原则:

- 地址线长度尽量一致,避免信号延迟差异。

- 避免与高频信号线(如时钟线)平行走线,减少串扰。

- 在多层PCB中,优先将地址线布放在同一信号层。

- 端接电阻:高频系统中,地址线末端可加47Ω~100Ω端接电阻,抑制信号反射。

不同存储器的连接差异

- SRAM/DRAM:

SRAM地址线直接连接,DRAM需配合行列地址复用,需通过控制器生成RAS/CAS信号。

- Flash存储器:

并行Flash地址线连接方式与SRAM类似;串行Flash(如SPI Flash)无需地址线,通过协议传输地址。

- EEPROM:

I²C或SPI接口的EEPROM通过总线协议寻址,无需独立地址线。

常见问题与解决方法

Q1:地址线数量不足怎么办?

- 方案1:使用地址译码器(如74HC138)扩展高位地址线,将存储器分为多个区块。

- 方案2:换用更大地址空间的存储器芯片。

Q2:地址线信号受干扰导致读写错误?

- 检查电源稳定性,增加去耦电容(如0.1μF陶瓷电容)在存储器电源引脚附近。

- 缩短地址线长度或使用差分信号(适用于高速系统)。

Q3:如何验证地址线连接正确?

- 用示波器或逻辑分析仪捕获地址线波形,检查信号跳变是否符合预期。

- 编写测试程序,向特定地址写入数据后读取校验。

地址线的连接需严格遵循硬件设计规范,重点关注电平匹配、信号完整性及布局优化,对于复杂系统,建议参考存储器数据手册和CPU参考设计,或使用成熟的开发板原理图作为模板。

引用说明

- 本文参考了《计算机组成与设计》(David A. Patterson, John L. Hennessy)、TI《Signal Integrity Basics》及常见存储器芯片手册(如Micron MT48LC64M4A2)。

- 部分实践经验来自嵌入式系统设计案例。