存储器体系中的哪一层才是速度瓶颈的关键所在?

- 行业动态

- 2025-04-29

- 3611

在计算机科学领域,存储器体系(Memory Hierarchy)是一套经过精密设计的系统,通过分层管理不同类型的存储设备,在速度、容量与成本之间实现最优平衡,它的存在解决了计算机系统中“存储墙”(Memory Wall)的核心矛盾——处理器运算速度远高于数据存取速度的瓶颈,以下是关于存储器体系的全面解析:

存储器体系的核心逻辑

存储器体系遵循“金字塔法则”:越靠近处理器的存储层级,容量越小、速度越快、成本越高;反之,容量越大、速度越慢、成本越低,这种分层结构利用时间局部性(频繁访问的数据近期可能再被使用)和空间局部性(数据常以相邻位置被访问)原理,使95%以上的数据需求在高速层级得到满足。

典型分层结构(由上至下):

寄存器(Register)

- 速度:0.3-1纳秒访问时间

- 容量:几十到几百字节

- 角色:直接与CPU交互,存放指令和运算数据

- 技术:静态随机存取存储器(SRAM)

高速缓存(Cache)

- 层级:L1(核心独享)、L2(核心共享)、L3(多核共享)

- 速度:L1约1纳秒,L3约10-20纳秒

- 容量:KB级至MB级

- 技术:SRAM,采用LRU(最近最少使用)等替换算法

主存(Main Memory,DRAM)

- 速度:50-100纳秒

- 容量:GB级(现代计算机标配8-64GB)

- 技术:动态随机存取存储器(DRAM),需周期性刷新

辅助存储(Secondary Storage)

- 类型:固态硬盘(SSD)、机械硬盘(HDD)、光盘

- 速度:SSD约50-150微秒,HDD约5-15毫秒

- 容量:TB级起步

- 技术:NAND闪存(SSD)、磁盘磁记录(HDD)

离线存储(Tertiary Storage)

- 示例:磁带库、云存储备份

- 特点:容量可达PB级,按需访问

存储器协同工作原理

缓存命中(Cache Hit)与缺失(Cache Miss)

当CPU请求数据时,首先在L1缓存中查找,若命中,直接读取;若缺失,逐级向L2、L3缓存和主存查询,缓存命中率每提升10%,系统整体性能可提高20-30%。虚拟内存机制

操作系统通过页表(Page Table)将主存与硬盘空间虚拟化为连续地址,利用分页技术(如4KB页大小)和页面置换算法(如Clock算法)扩展可用内存。预取(Prefetching)技术

现代CPU通过分析访问模式,提前将可能使用的数据加载到缓存中,例如Intel的Adjacent Cache Line Prefetch技术可预判连续地址访问。

关键技术演进与创新

新型存储介质

- 3D XPoint(Optane):英特尔与美光联合研发,速度介于DRAM与SSD之间,可作持久化内存(Persistent Memory)。

- Z-NAND:三星推出的低延迟闪存,擦写次数是普通TLC的10倍。

存储级内存(Storage-Class Memory,SCM)

结合DRAM的速度与SSD的非易失性,打破传统内存-存储二分法,典型应用包括数据库加速和实时分析系统。异构内存架构(HMA)

在服务器领域,DDR4与高带宽内存(HBM)混合使用,HBM通过3D堆叠技术实现超过400GB/s带宽,适合AI训练等高吞吐场景。

存储器体系的优化策略

软件层优化

- 数据对齐(Data Alignment):确保数据结构匹配缓存行(通常64字节),减少跨行访问。

- 循环分块(Loop Tiling):将大数据集拆分为适合缓存的块,提升局部性。

硬件层创新

- 非一致性缓存架构(NUCA):将大容量缓存划分为多个区域,物理靠近不同处理器核心。

- 缓存感知调度(Cache-Aware Scheduling):操作系统根据缓存状态分配线程,降低争用。

量子存储技术(前瞻性)

量子计算机需匹配量子存储器,目前超导电路与离子阱方案可实现微秒级量子比特保存,未来可能颠覆经典存储体系。

存储器体系对实际应用的影响

消费电子领域

- 智能手机采用UFS 3.1闪存,顺序读写速度达2000MB/s,接近SATA SSD水平。

- 游戏主机(如PS5)通过定制SSD实现5.5GB/s吞吐,消除开放世界游戏加载延迟。

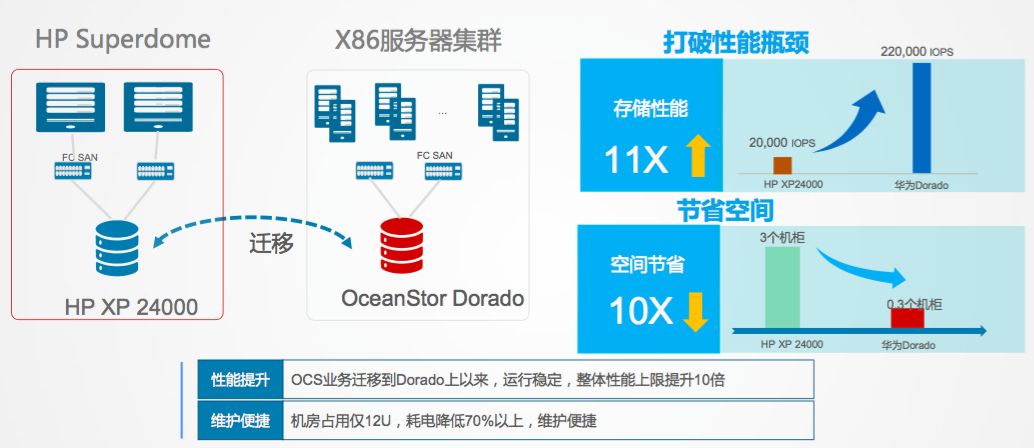

数据中心场景

- 内存数据库(如Redis):完全运行于内存,响应时间低于1毫秒。

- 冷热数据分层:热数据存于NVMe SSD,冷数据迁移至QLC SSD或磁带库。

边缘计算趋势

边缘设备(如自动驾驶控制器)采用LPDDR5X内存,功耗比DDR4低30%,带宽达8533Mbps,满足实时决策需求。

未来挑战与发展方向

- 能效比提升:DRAM功耗占数据中心总能耗的15%,需通过DDR5低电压(1.1V)和3D封装技术优化。

- 存算一体(In-Memory Computing):在存储单元内完成计算,减少数据搬运,谷歌TPUv4已试点应用。

- 光子存储器:利用光子代替电子传输数据,实验室原型速度达100GHz,延迟降低90%。

引用说明

- Hennessy, J. L., & Patterson, D. A. (2017). Computer Architecture: A Quantitative Approach (6th ed.). Morgan Kaufmann.

- Wikipedia contributors. (2025). Memory hierarchy. Wikipedia.

- Samsung Electronics. (2022). Z-NAND Technology White Paper.

- Intel Corporation. (2021). 3D XPoint Memory Technology Overview.