上一篇

存储器设计如何突破性能极限?

- 行业动态

- 2025-04-28

- 3389

存储器设计需兼顾存储单元结构、读写速度、功耗及可靠性,通过电路优化与工艺创新提升容量和性能,关键技术在DRAM、SRAM、闪存等类型中实现差异化平衡,新兴非易失性存储器采用相变、阻变等材料突破传统局限,同时需针对应用场景优化架构,满足高速计算与低功耗物联网需求。

存储器的分类与技术原理

存储器按特性可分为易失性存储器和非易失性存储器两类:

易失性存储器(Volatile Memory)

- DRAM:动态随机存取存储器,利用电容存储电荷,需要定期刷新

- SRAM:静态随机存取存储器,基于触发器电路,速度快但成本高

- 典型应用:计算机内存、处理器缓存

非易失性存储器(Non-Volatile Memory)

- NAND Flash:通过浮栅晶体管存储数据,主流固态存储介质

- NOR Flash:支持随机访问,常用于嵌入式系统固件

- 新型存储器:3D XPoint(傲腾)、RRAM(阻变存储器)等

存储器设计的核心要素

存储单元结构设计

- 晶体管尺寸优化:14nm/10nm FinFET工艺的应用

- 三维堆叠技术:如3D NAND的垂直通道结构

- 电荷保持机制:DRAM刷新周期的计算模型

存取电路设计

- 灵敏放大器(Sense Amplifier)的噪声抑制

- 行列译码器的低功耗设计

- 读写时序的精准控制(tRCD/tRP/tRAS参数)

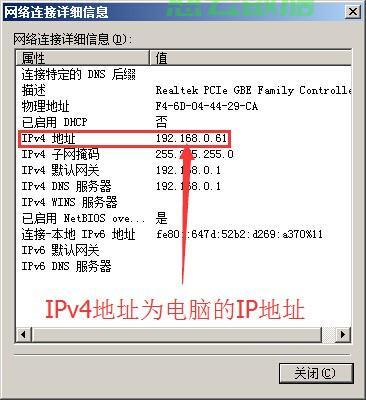

接口与协议

- DDR5标准:4800MT/s传输速率与双通道架构

- PCIe 5.0接口:32GT/s带宽支持高速存储

- ONFI 4.2协议:Toggle Mode提升NAND吞吐量

存储器设计全流程

架构设计阶段

- 容量规划与bank划分策略

- 并行存取路径的拓扑结构

- 纠错码(ECC)方案选择:BCH码 vs LDPC码

电路仿真验证

- SPICE模型仿真:验证单元读写特性

- 时序分析:建立/保持时间裕量计算

- 功耗模拟:动态功耗与漏电流优化

物理实现阶段

- 布局布线(Place & Route)优化

- 信号完整性分析:串扰与IR drop控制

- 测试结构设计:BIST(内建自测试)电路集成

先进存储技术解析

3D存储技术

- 三星V-NAND:128层堆叠,CTF(电荷捕获闪存)结构

- 美光CuA(CMOS under Array)架构:逻辑电路底层集成

新型存储介质

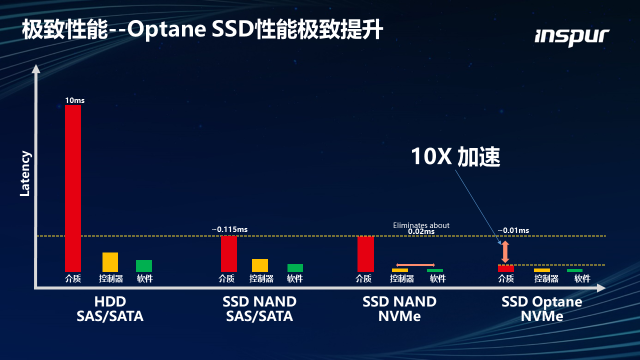

- 相变存储器(PCM):Intel Optane的Ovonyx技术

- 磁阻存储器(MRAM):STT-MTJ(自旋转移矩磁隧道结)

存算一体技术

- 近存计算:HBM(高带宽内存)与GPU协同

- 存内计算:利用ReRAM实现矩阵运算加速

设计挑战与解决方案

| 挑战类型 | 具体问题 | 行业解决方案 |

|---|---|---|

| 物理极限 | 量子隧穿效应 | 高k介质材料(如HfO₂) |

| 信号衰减 | 位线电压降 | 分级位线结构设计 |

| 制程变异 | 工艺偏差影响 | 自适应纠偏电路 |

| 散热问题 | 3D堆叠热积聚 | TSV硅穿孔散热通道 |

未来发展趋势

工艺演进路线

- DRAM:1β节点EUV光刻技术应用

- NAND:QLC/PLC高密度存储发展

- 新型存储器:FeFET(铁电晶体管)技术突破

系统级创新

- CXL(Compute Express Link)内存共享协议

- 存算一体芯片:清华大学忆阻器芯片成果

- 光子存储器:硅光互连技术研发进展

能效比提升

- 低电压操作:0.4V亚阈值电路设计

- 自适应刷新:AI预测的DRAM刷新策略

- 非易失内存:NVDIMM持久化内存架构

参考资料:

- 《半导体存储器技术》(科学出版社,2022)

- IEEE Transactions on Electron Devices: “3D NAND Design Challenges”

- JEDEC协会DDR5标准文档(JESD79-5B)

- Yole Développement《2025年存储器行业报告》

- 三星、美光、铠侠等公司技术白皮书