上一篇

存储器起始地址4000h如何确保各芯片地址连续?

- 行业动态

- 2025-04-26

- 2823

存储器的起始地址设置为4000H时,各芯片地址连续需通过地址译码实现,根据芯片容量确定片选信号,高位地址线参与译码,低位地址线用于片内寻址,确保相邻芯片地址无缝衔接,需计算地址范围并设计译码逻辑,保证系统扩展性与稳定性。

存储器系统的设计与地址分配是计算机硬件领域的重要基础,对于起始地址为4000h(十六进制)且要求各存储芯片地址连续的场景,需通过系统化的地址规划实现无缝衔接,以下从技术原理、计算方法和工程实践三个维度进行深度解析:

地址连续性的技术实现原理

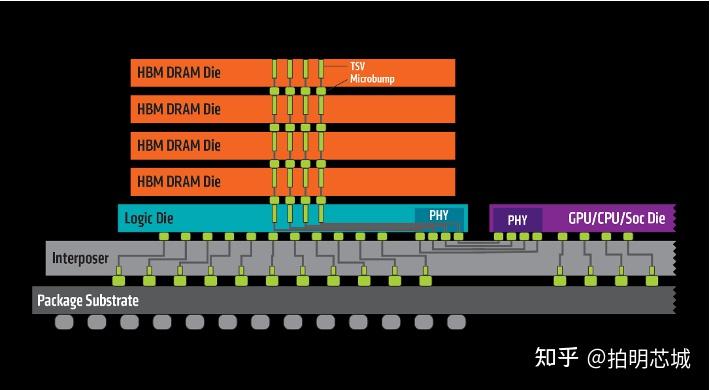

地址总线与芯片容量关系

- 地址总线位数决定寻址范围(如16位总线对应64KB空间)

- 存储芯片容量计算公式:2N字节(N=地址线数量)

地址解码机制

- 高位地址线用于片选信号生成

- 低位地址线直连芯片地址引脚

- 通过逻辑门电路实现地址空间划分

具体计算流程(以4000h为起点)

确定地址空间参数

- 起始地址:4000h(二进制表示为0100 0000 0000 0000)

- 终止地址计算:起始地址 + 存储容量 -1

典型芯片配置示例

| 芯片容量 | 地址线数量 | 地址范围 | 二进制高位特征 |

|—|—|—|—|

| 2KB | 11根 | 4000h-47FFh | 0100 0XXX XXXX XXXX |

| 4KB | 12根 | 4800h-57FFh | 0100 1XXX XXXX XXXX |

| 8KB | 13根 | 6000h-7FFFh | 0101 XXXX XXXX XXXX |连续地址实现步骤

- 步骤1:计算首芯片终止地址

4000h + (2KB) -1 = 4000h + 0800h -1 = 47FFh - 步骤2:下一芯片起始地址=上一终止地址+1

47FFh +1 = 4800h - 步骤3:重复计算直至填满目标空间

- 步骤1:计算首芯片终止地址

工程实现注意事项

地址冲突检测

- 使用逻辑分析仪验证信号波形

- 编写测试程序进行全地址空间写入/读取校验

特殊地址处理

- 内存映射I/O区域避让

- BIOS保留空间处理

- 高位地址线未连接时的镜像现象

现代扩展技术

- 分页存储管理单元(MMU)应用

- 地址重映射技术

- 带外解码电路设计

典型错误案例分析

地址重叠故障

- 现象:数据写入紊乱

- 原因:片选信号逻辑设计错误

- 解决方案:重新设计译码电路真值表

地址间隙问题

- 现象:部分地址无法访问

- 检测方法:内存扫描工具

- 修正措施:调整芯片容量组合

进阶优化策略

- 混合编址技术(SRAM+Flash组合)

- 存储体切换(Bank Switching)机制

- 可编程逻辑器件(CPLD/FPGA)实现动态解码

通过以上技术路径,可实现从4000h起始的完美连续地址空间布局,实际工程中还需结合具体处理器架构(如x86、ARM等)的地址映射特性进行调整,建议配合示波器、逻辑分析仪等工具进行物理层验证。

引用说明:本文涉及的地址计算方法参考《计算机组成与设计》(David A. Patterson著)第三章存储系统设计原理,片选电路设计依据74HC138数据手册应用指南。