如何轻松制作存储器?这几点秘诀你肯定不知道!

- 行业动态

- 2025-05-01

- 5

从硅片到数据核心的技术之旅

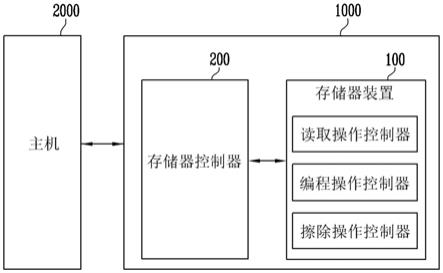

存储器是数字时代的基石,无论是手机、电脑,还是数据中心,其性能与可靠性直接取决于存储器的设计与制造水平,本文将深入解析存储器的制作流程、核心技术及行业趋势,揭开这一精密科技背后的奥秘。

存储器的分类与基础材料

存储器分为易失性存储器(如DRAM)和非易失性存储器(如NAND闪存、3D XPoint),它们的核心材料均为半导体级硅(Silicon),纯度高达99.9999999%(9N)。

- 硅晶圆:通过提拉法(Czochralski法)制成单晶硅锭,切割为厚度约0.7mm的晶圆片。

- 功能层材料:如氮化硅(SiN)用于绝缘,多晶硅(Poly-Si)用于晶体管栅极,铜(Cu)或钴(Co)用于互联导线。

- 新兴材料:相变存储器(PCM)中的锗锑碲(GeSbTe)合金、阻变存储器(ReRAM)的氧化铪(HfO₂)等。

存储器制造的八大核心步骤

光刻(Photolithography)

利用深紫外光(DUV)或极紫外光(EUV)在晶圆上刻出纳米级电路图案,EUV技术可实现7nm以下制程,是3D NAND和DRAM微缩化的关键。

示例:三星的V-NAND通过堆叠128层存储单元,将容量提升至1Tb以上。蚀刻(Etching)

干法蚀刻(如等离子体蚀刻)精准去除多余材料,形成三维结构,3D NAND的垂直通道蚀刻需控制深度与均匀性,误差需小于1nm。

薄膜沉积(Deposition)

化学气相沉积(CVD)和原子层沉积(ALD)技术逐层堆叠氧化物、氮化物,构建存储单元,ALD的膜厚控制精度可达原子级别。离子注入(Ion Implantation)

将硼(B)、磷(P)等元素注入硅中,调节晶体管的导电性,能量与角度的精准控制决定器件性能。化学机械抛光(CMP)

通过研磨液与抛光垫的协同作用,使晶圆表面平坦化,确保多层堆叠无偏差。互连(Interconnect)

采用铜互连(Cu Interconnect)或钴互连技术,减少电阻并提升信号传输速度,双镶嵌工艺(Dual Damascene)是主流方法。封装与测试(Packaging & Testing)

- 封装:将晶圆切割为芯片后,采用TSV(硅通孔)或Fan-Out工艺封装,提升密度与散热能力。

- 测试:通过探针台(Prober)进行功能测试,筛选合格产品,良率通常需高于95%。

质量控制与可靠性验证

高温老化测试(Burn-in)、数据保持力测试(Data Retention)确保产品在极端环境下的稳定性。

行业核心技术突破

3D堆叠技术

美光(Micron)的232层NAND和SK海力士的238层DRAM标志着存储密度的飞跃,通过垂直堆叠单元降低单位成本。EUV光刻机的应用

ASML的EUV光刻机波长仅13.5nm,台积电(TSMC)和英特尔(Intel)借此实现5nm以下逻辑芯片与存储器的协同制造。存储级内存(SCM)

英特尔傲腾(Optane)结合DRAM的速度与NAND的非易失性,延迟低至10微秒,革新数据中心架构。

市场现状与未来挑战

- 市场规模:2025年全球存储器市场达1500亿美元,DRAM占比55%,NAND占40%(数据来源:TrendForce)。

- 技术瓶颈:随着工艺逼近物理极限,量子隧穿效应和热噪声成为3nm以下制程的主要障碍。

- 绿色制造:半导体耗水量大,台积电的“零废液排放”技术和再生晶圆使用率提升至60%以上,成为行业标杆。

存储器制造是材料科学、精密工程与算法优化的集大成者,从一粒沙到存储芯片,背后是数千道工序的极致追求,随着AI、自动驾驶对数据需求的爆发,存储器的创新将决定未来十年数字社会的天花板。

参考文献

- International Roadmap for Devices and Systems (IRDS) 2022

- IEEE Transactions on Electron Devices: “3D NAND Technology Challenges”

- SEMI Industry Research Reports 2025

- ASML官网技术白皮书