反复刷新的存储器为

- 行业动态

- 2025-05-03

- 2

动态随机存取存储器(DRAM)

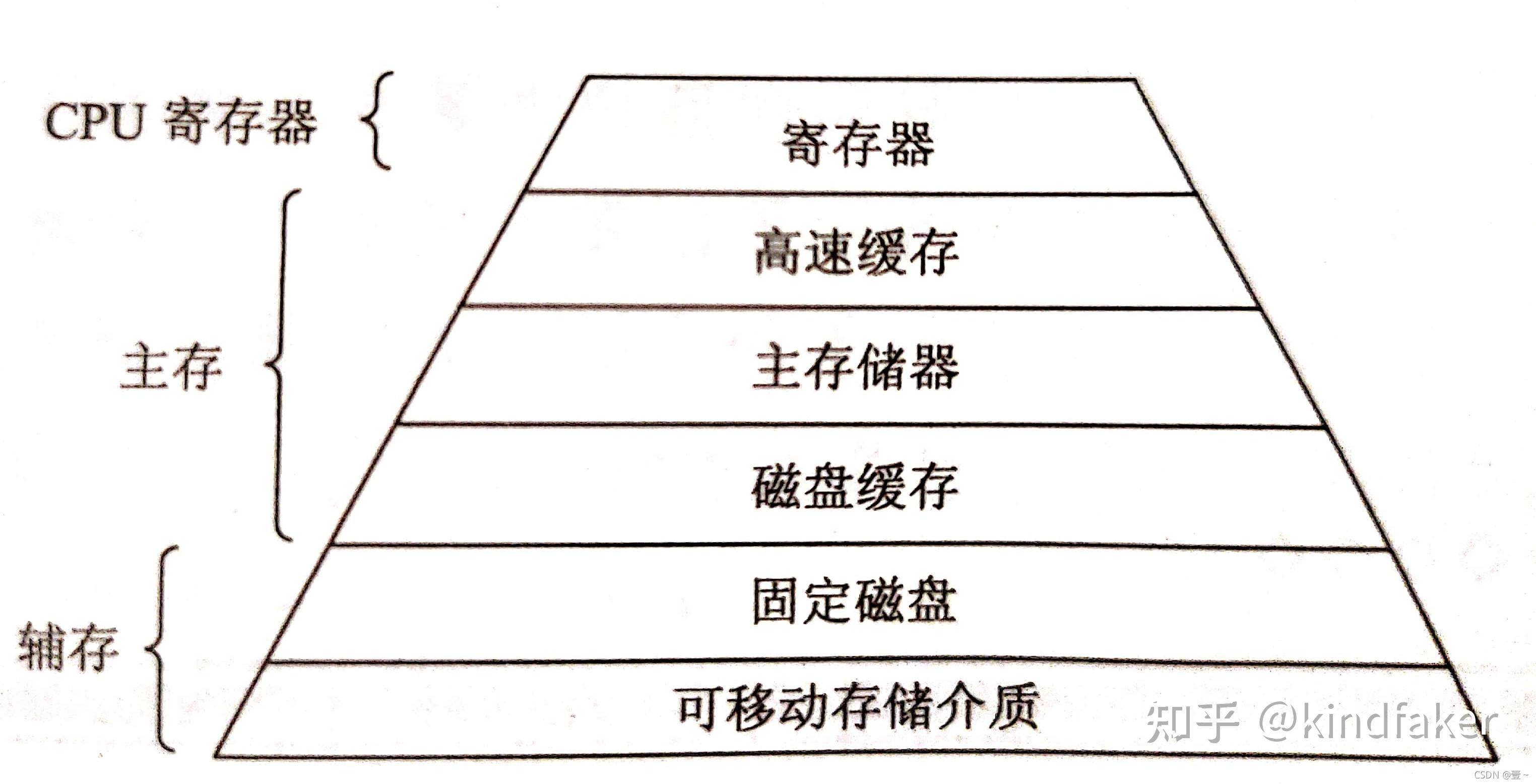

存储器分类与基本原理

现代计算机系统中,存储器根据存储特性可分为易失性存储器和非易失性存储器两大类:

| 类别 | 代表类型 | 是否需要刷新 | 断电后数据保留 | 典型用途 |

|—————-|—————————|——————|——————–|————————|

| 易失性存储器 | DRAM、SRAM | DRAM需要 | 否 | 主存、缓存 |

| 非易失性存储器 | ROM、Flash、硬盘、SSD | 无需 | 是(部分类型) | 固件存储、长期数据保存 |

动态随机存取存储器(DRAM)因其高密度和低成本,成为计算机主存的核心组件,但其存储单元依赖电容电荷保存数据,电荷会随时间泄漏,必须通过周期性刷新维持数据。

DRAM的结构与工作原理

DRAM的基本存储单元由一个晶体管和一个电容构成(如图1),电容存储电荷表示二进制数据(充电为1,放电为0),晶体管负责读写操作,由于电容存在漏电问题,数据只能在几毫秒级时间内保持,因此需要刷新机制。

表1:DRAM与SRAM核心对比

| 特性 | DRAM | SRAM |

|---|---|---|

| 存储单元 | 1晶体管+1电容 | 6晶体管(触发器结构) |

| 密度 | 高(适合大容量内存) | 低(用于高速缓存) |

| 功耗 | 较低(仅刷新时耗电) | 较高(持续供电) |

| 速度 | 较慢(需等待刷新周期) | 快(无需刷新) |

| 成本 | 低 | 高 |

DRAM的刷新机制详解

刷新的必要性

DRAM电容的电荷泄漏会导致数据丢失,典型情况下,数据在64ms内必须刷新一次(如DDR4标准),否则会出现位错误。刷新操作类型

- 全局刷新:中断正常操作,逐行刷新所有存储单元。

- 分布式刷新:将刷新操作分散在多个周期中,减少对性能的影响。

- 自刷新:在休眠模式下降低刷新频率(如每秒一次),节省功耗。

刷新流程

- 行地址选中:刷新控制器按行地址依次访问存储阵列。

- 数据重写:读出原数据后重新写入,补充电容电荷。

- 计数器调度:通过内置计数器跟踪刷新周期,确保全覆盖。

刷新对性能的影响

带宽占用

刷新操作会暂时占用内存总线,导致正常读写请求被延迟,DDR4内存每64ms刷新8192行(8GB内存),每次刷新占用数百纳秒,累计占用约1%~1%的带宽。功耗分布

刷新能耗占DRAM总功耗的10%~20%,但在高性能场景(如高频DDR5)中,这一比例可能上升。优化策略

- 智能调度:利用空闲周期执行刷新。

- 温度补偿:高温下加快刷新频率以降低漏电风险。

- 低功耗模式:在待机时切换自刷新模式。

其他存储器的对比分析

| 存储器类型 | 是否需要刷新 | 数据持久性 | 典型容量 | 速度 | 成本 |

|---|---|---|---|---|---|

| DRAM | 是 | 易失 | MB~GB级 | 快(纳秒级) | 低 |

| SRAM | 否 | 易失 | KB~MB级 | 极快(1-10ns) | 高 |

| NAND Flash | 否 | 非易失 | GB~TB级 | 较慢(微秒级) | 中 |

| NOR Flash | 否 | 非易失 | MB~GB级 | 慢(百微秒级) | 中 |

实际应用中的典型场景

计算机主存

DRAM作为主存的核心,承担操作系统、运行程序的数据存储,其高密度和低成本使其成为大容量内存的唯一选择,但需依赖刷新维持数据。显卡显存

GPU使用GDDR(Graphics DDR)显存,同样基于DRAM架构,但优化了带宽和频率,刷新机制与主存类似。嵌入式系统

在低功耗设备(如智能手表)中,DRAM可能被替换为无需刷新的eDRAM(嵌入式DRAM),但其成本较高。

FAQs

问题1:为什么DRAM需要刷新,而SRAM不需要?

答:DRAM依赖电容存储电荷,电荷会因漏电逐渐消失,必须周期性刷新以维持数据,而SRAM使用触发器(多晶体管结构)存储数据,只要供电正常即可持续保存,无需刷新。

问题2:如果停止对DRAM的刷新会发生什么?

答:未及时刷新会导致电容电荷完全泄漏,存储的数据逐渐丢失,停止刷新后,DRAM内容可能在几百毫秒到一秒内出现大量错误,导致