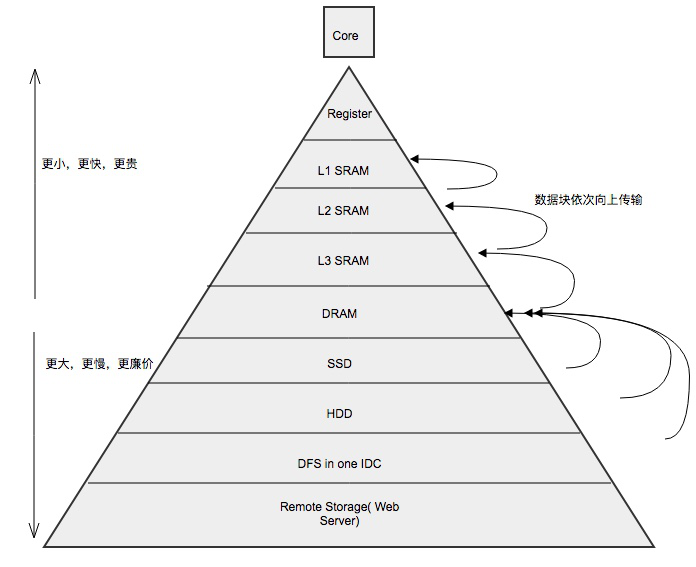

在计算机系统与高性能计算领域,“存储器山”(Memory Mountain)是一个直观且重要的性能分析模型,它通过图形化方式揭示计算机内存系统的层次结构(如缓存、主存等)对程序运行效率的影响,帮助开发者理解不同存储层级的访问速度与容量之间的关系。

<section>

<h3>存储器山的核心价值</h3>

<ul>

<li><strong>可视化存储层级瓶颈</strong>:存储器山模型以“时间”为纵轴、“数据量”为横轴,展示程序访问不同容量数据时的延迟变化,随着数据量超过缓存容量,延迟急剧上升形成“陡坡”,清晰指出性能拐点。</li>

<li><strong>指导代码优化方向</strong>:通过观察存储器山的“山脚”与“山峰”,开发者可判断程序是否充分利用缓存,并针对性优化数据局部性(如调整循环顺序、分块处理数据)。</li>

<li><strong>硬件选型参考依据</strong>:对比不同处理器/内存配置下的存储器山形态,可评估设备是否匹配应用场景(如高频交易需陡峭山脚,科学计算需平缓山坡)。</li>

</ul>

</section>

<section>

<h3>典型应用场景</h3>

<div class="case-box">

<div class="case-item">

<p class="case-title">▍高性能计算(HPC)</p>

<p>优化矩阵运算时,通过存储器山测试确定最佳分块大小,使计算核心始终从高速缓存读取数据,避免频繁访问主存。</p>

</div>

<div class="case-item">

<p class="case-title">▍数据库系统</p>

<p>设计索引结构时,结合存储器山分析热点查询的数据量,确保高频访问的数据集能被L3缓存容纳,降低I/O延迟。</p>

</div>

</div>

</section>

<section>

<h3>如何利用存储器山提升性能?</h3>

<ol>

<li><strong>测试基准建立</strong>:使用工具(如Intel® MLC、STREAM)测量不同工作集大小下的内存带宽与延迟,绘制初始存储器山曲线。</li>

<li><strong>瓶颈定位</strong>:观察曲线上出现显著延迟上升的点,对应缓存层级容量(如L1:32KB、L2:256KB、L3:30MB)。</li>

<li><strong>优化策略实施</strong>:<br>

- 重构数据结构,减少缓存行未命中(Cache Miss)<br>

- 采用缓存感知算法(Cache-Oblivious Algorithm)<br>

- 调整线程绑定,避免多核竞争缓存资源</li>

</ol>

</section>

<section class="expert-insight">

<blockquote>

<p>“存储器山的价值在于将抽象的存储性能转化为可操作的工程指标,在DDR5与3D堆叠缓存普及的今天,这一模型仍是平衡算力与存储墙矛盾的核心工具。”<br>—— John L. Hennessy,图灵奖得主,《计算机体系结构》合著者</p>

</blockquote>

</section>

<section>

<h3>未来演进方向</h3>

<p>随着新型存储技术(如CXL内存池、存算一体芯片)的发展,存储器山模型正在扩展:</p>

<table>

<tr><th>技术趋势</th><th>对存储器山的影响</th></tr>

<tr><td>异构内存架构</td><td>山脉呈现多峰形态,需区分DRAM/PMem访问特征</td></tr>

<tr><td>近内存计算</td><td>特定计算任务可在“山腰”直接执行,突破传统存储墙</td></tr>

</table>

</section>

<section class="references">

<p>参考文献:<br>

1. Hennessy J L, Patterson D A. Computer Architecture: A Quantitative Approach[M]. 6th ed. Morgan Kaufmann, 2017.<br>

2. Intel® Memory Latency Checker工具白皮书, 2022</p>

</section>