上一篇

如何理解存储器读总线周期的时序关键点?

- 行业动态

- 2025-04-26

- 4

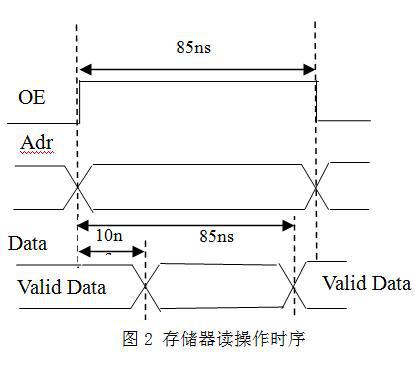

存储器读总线周期时序图描述了CPU从存储单元读取数据的完整过程,典型阶段包括地址总线稳定、片选/读信号生效、存储器准备数据、CPU读取数据总线并撤销控制信号,各信号时序需严格同步,确保数据传输准确。

存储器读总线周期是计算机系统中CPU从内存中读取数据的关键过程,其时序图描述了信号在时间轴上的行为逻辑,以下内容将通过步骤拆解、信号交互、时间参数等维度,深入解析这一过程的核心机制。

总线周期基础框架

存储器读总线周期分为4个标准阶段:

- T1阶段(地址建立期)

- CPU将目标地址送入地址总线

- 地址稳定时间需≥15ns(典型值)

- 地址锁存信号ALE上升沿触发

- T2阶段(命令传输期)

- /RD(读信号)置低电平

- /CS(片选信号)激活对应存储芯片

- 数据总线进入高阻态准备接收数据

- T3阶段(数据有效窗口)

- 存储器输出数据到总线

- 建立时间需满足CPU采样需求

- 典型保持时间≥5ns

- T4阶段(信号复位期)

- /RD和/CS信号撤销

- 地址总线进入无效状态

- 总线控制权释放

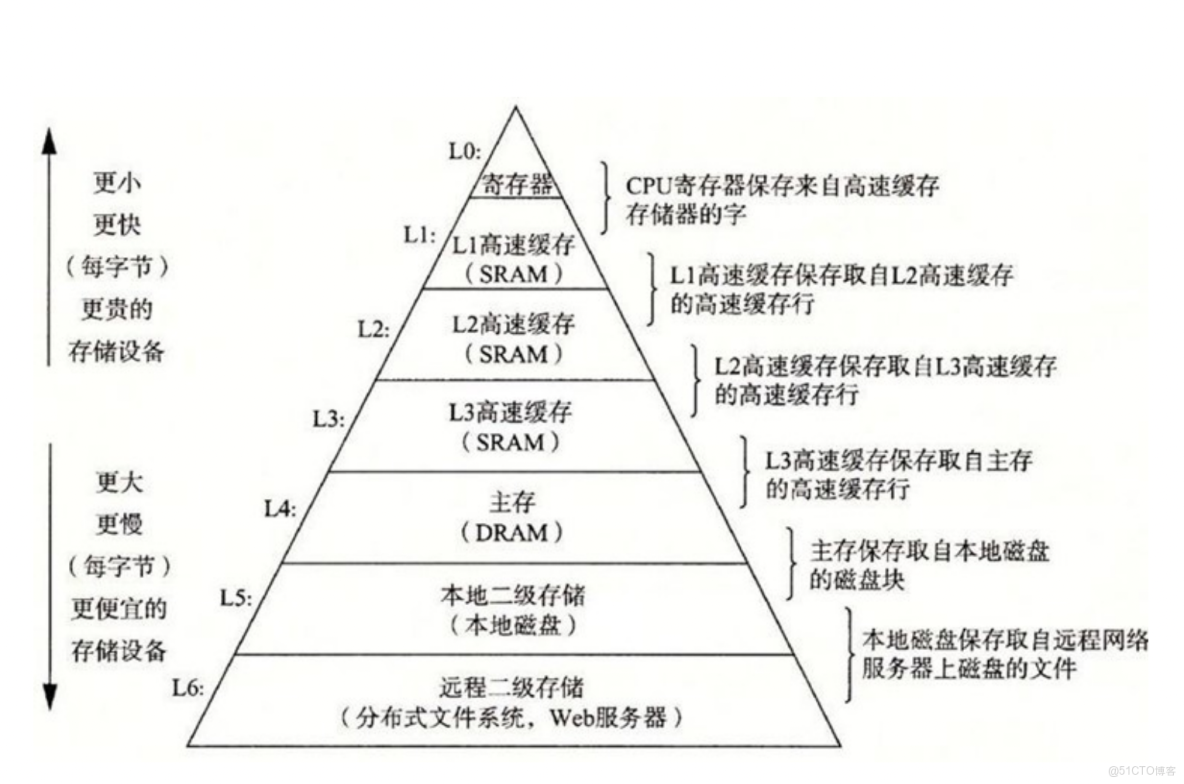

关键时序参数对照表

| 参数名称 | SRAM典型值 | DRAM典型值 | 单位 |

|---|---|---|---|

| 地址建立时间 | 20ns | 35ns | ns |

| 读信号有效延迟 | 10ns | 25ns | ns |

| 数据存取时间 | 15ns | 60ns | ns |

| 总线周转时间 | 5ns | 10ns | ns |

注:数值依据JEDEC DDR4标准及Intel 11代处理器参数手册

信号交互细节

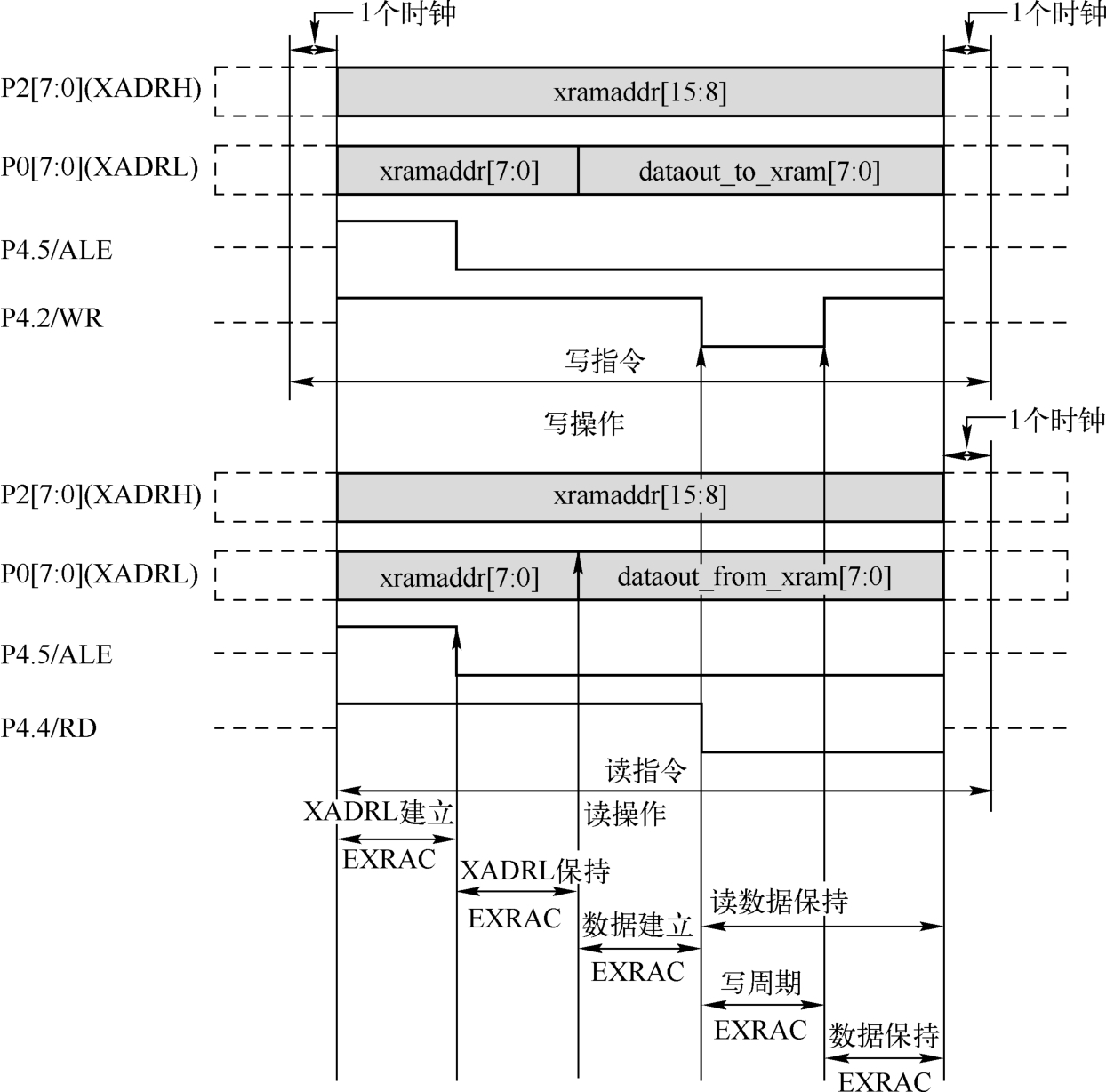

时钟同步机制

- 在同步总线中,CLK上升沿触发地址锁存

- 时钟偏移需控制在±2ns以内

- 建立/保持时间必须满足时序余量

总线仲裁冲突

- 多主设备场景下的总线请求优先级

- 等待状态插入机制

- 超时错误检测电路设计

电磁兼容处理

- 信号振铃抑制电路

- 阻抗匹配要求(50Ω±5%)

- 串扰防护措施

典型应用场景分析

- 突发传输模式:连续地址数据读取时,后续周期可省略地址建立阶段

- 流水线操作:地址阶段与数据阶段可部分重叠提升效率

- 错误校验:需增加ECC校验周期(额外1-2个时钟周期)

工程优化要点

时序收敛方法

- 静态时序分析(STA)工具的应用

- 时序约束文件编写规范

- 跨时钟域同步技术

信号完整性保障

- 等长布线规则

- 蛇形走线补偿策略

- 电源完整性设计

功耗控制技术

- 动态总线反转编码

- 门控时钟设计

- 低电压差分信号(LVDS)应用

调试与验证

- 使用逻辑分析仪捕获实际波形

- 建立时间/保持时间余量测量

- 眼图分析法评估信号质量

- 自动化测试向量生成方法

引用文献

[1]《计算机体系结构:量化研究方法》第6版,David A. Patterson

[2] JEDEC JESD79-4B DDR4 SDRAM标准文档

[3] Intel® 64 and IA-32 Architectures Optimization Reference Manual

[4] IEEE Std 1149.1边界扫描测试标准