上一篇

随机存储方式为何成为数据存取速度的关键?

- 行业动态

- 2025-05-01

- 2

随机存储方式允许直接访问存储器中的任意位置,数据读取速度与存储位置无关,其通过唯一地址精准定位,支持快速读写操作,适用于需要高效数据调用的场景,典型代表为随机存取存储器(RAM),具备易失性,断电后数据丢失,广泛用于计算机主存和高速缓存。

在计算机系统中,存储器是实现数据存取的核心部件,而随机存储方式(Random Access Memory, RAM)作为其中的关键技术,直接影响设备的运行效率,本文将系统解析随机存储的运作机制、技术分类及实际应用价值,帮助读者深入理解这一基础但至关重要的概念。

什么是随机存储?

随机存储方式的核心特征是直接访问任意存储单元的能力,无论是读取还是写入数据,存储控制器无需按顺序遍历其他位置,仅需通过地址信号即可在相同时间内定位目标位置,这一特性与顺序存储(如磁带)形成鲜明对比,后者必须按物理顺序逐个访问。

技术特点总结:

- 地址独立性:每个存储单元对应唯一地址

- 均等时间访问(Uniform Access Time):访问时间与数据位置无关

- 易失性:主流RAM需持续供电维持数据(例外:非易失性RAM技术)

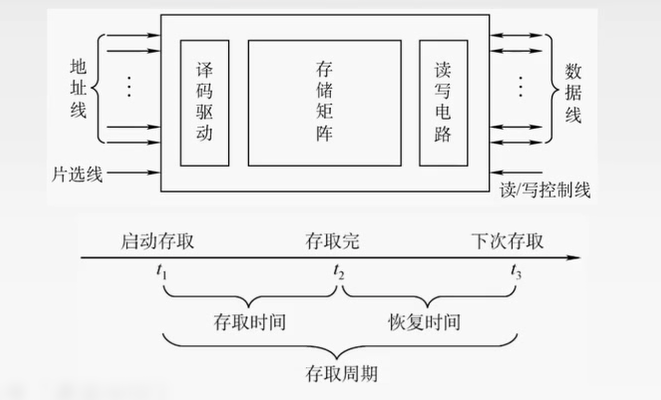

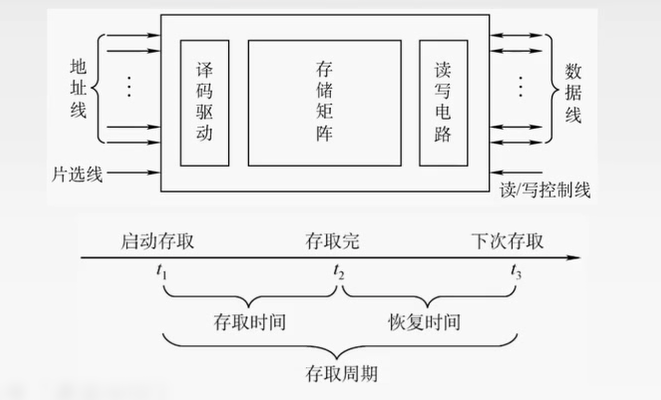

随机存储的物理实现原理

现代RAM芯片通过晶体管-电容结构阵列实现数据存储,以经典的DRAM为例:

- 存储单元:由1个晶体管+1个电容构成

- 电荷状态判定:电容充满代表1,放空代表0

- 刷新机制:因电容漏电,需要每64ms执行刷新周期

关键技术参数:

- 存取速度:现代DDR5 RAM达6.4Gbps

- 密度:3D堆叠技术实现单芯片24Gb容量

- 能效:LPDDR5将功耗降至1.1V

主流随机存储技术对比

| 类型 | DRAM | SRAM | NVMe over RAM |

|---|---|---|---|

| 结构 | 晶体管+电容 | 6晶体管锁存器 | 闪存控制器+电容备份 |

| 刷新需求 | 需要 | 不需要 | 仅断电时触发 |

| 速度 | 50-100ns | 10ns级 | 微秒级 |

| 成本/bit | $0.02 | $0.5 | $0.15 |

| 典型应用 | 内存条 | CPU缓存 | 工业控制系统 |

行业演进趋势:

- 3D封装:美光推出的3D XPoint技术将存储密度提升10倍

- 存算一体:三星HBM-PIM在内存中集成AI计算单元

- 新型介质:铪基铁电存储器(FeRAM)突破传统物理限制

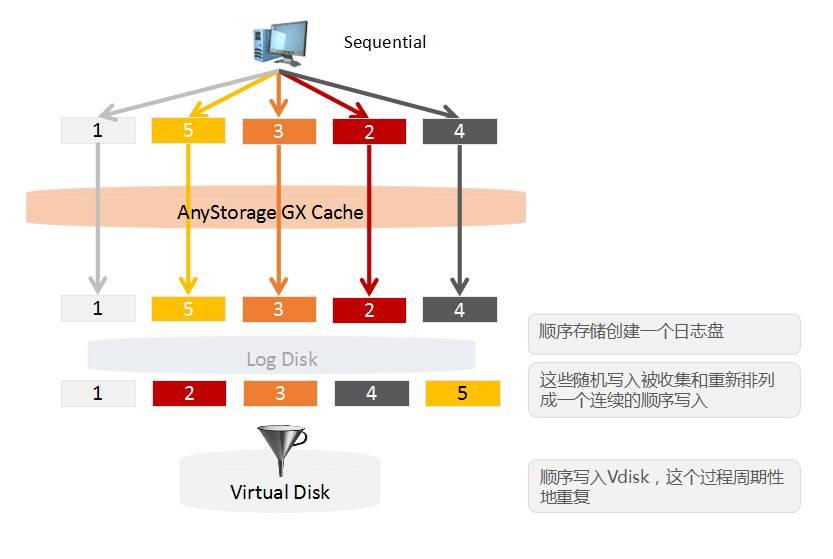

系统级优化实践

在数据中心场景中,工程师通过分层存储架构最大化随机存储效能:

CPU寄存器 → SRAM缓存 → DRAM主存 → NAND闪存

优化策略案例:

- NUMA架构:将内存控制器分布在多CPU节点,降低访问延迟

- 内存虚拟化:VMware ESXi通过透明页共享提升内存利用率

- 持久化内存:Intel Optane DC PMEM实现DRAM级速度的持久存储

技术挑战与突破方向

- 漏电难题:7nm以下工艺节点漏电率达23%,台积电通过high-κ介质改进

- 散热限制:HBM2e内存堆叠导致热密度达200W/cm²,液冷方案已成标配

- 安全破绽:Rowhammer攻击可通过高频访问引发比特翻转,需硬件级防护

国际半导体路线图(IRDS)预测:到2028年,新型磁阻RAM(MRAM)将逐步替代部分DRAM市场,实现纳秒级非易失存储。

选型指南(企业级场景)

- 实时交易系统:选择SRAM缓存+ECC DRAM组合

- AI训练集群:配置HBM2e显存+3D堆叠DRAM

- 边缘计算:采用LPDDR5X搭配PMIC电源管理芯片

性能测试数据:

- DDR5-6400对比DDR4-3200:带宽提升118%,延迟降低18%

- 3D堆叠DRAM:单位面积容量达传统设计的8倍

权威引用

- 《计算机体系结构:量化研究方法》第6版,John L. Hennessy等,2020年

- JEDEC固态技术协会发布DDR5标准(JESD79-5B)

- 国际固态电路会议(ISSCC 2025)三星技术白皮书

- IEEE Transactions on Electron Devices关于3D NAND的可靠性研究