存储器映射I/O如何提升计算机性能

- 行业动态

- 2025-04-25

- 1

计算机系统中,存储器映射I/O(Memory-Mapped I/O,MMIO)是一种将输入输出设备(如键盘、网卡、GPU等)的控制寄存器或数据缓冲区映射到系统内存地址空间的技术,通过这种方式,CPU可以像访问普通内存一样直接操作硬件设备,无需专用指令,这种设计不仅简化了编程模型,还提升了系统灵活性,被广泛应用于现代计算机架构中。

存储器映射I/O的原理

在传统的计算机架构中,CPU与外部设备通信有两种主要方式:

- 端口映射I/O(Port-Mapped I/O,PMIO):通过专用指令(如

IN和OUT)访问设备的独立地址空间。 - 存储器映射I/O(MMIO):将设备的寄存器映射到内存地址,通过常规的

LOAD和STORE指令读写。

存储器映射I/O的核心实现步骤:

- 操作系统在初始化阶段为硬件设备分配一段物理内存地址。

- 设备寄存器或缓冲区被映射到该地址范围。

- CPU通过访问这些地址直接与设备交互,例如写入控制命令或读取状态信息。

一块显卡的显存可能被映射到内存地址0xA0000000至0xAFFFFFFF,程序向该区域写入数据时,实际是向显卡发送图像信息。

存储器映射I/O的优缺点

优势

- 编程简化:开发者无需学习特殊指令,使用普通内存操作即可控制硬件。

- 灵活性高:允许设备寄存器像普通变量一样参与地址计算(如指针操作)。

- 性能优化:某些场景下,内存总线的带宽和延迟优于专用I/O总线。

局限性

- 地址冲突风险:若内存映射范围规划不当,可能导致设备与内存地址重叠。

- 缓存一致性问题:CPU缓存可能缓存映射的I/O地址,需通过

volatile关键字或显式刷新机制避免数据错误。 - 安全性挑战:错误的指针操作可能意外修改设备状态,引发系统崩溃。

存储器映射I/O的典型应用

嵌入式系统

在资源受限的嵌入式设备(如单片机、IoT设备)中,存储器映射I/O是主流方案。

- ARM Cortex-M系列处理器通过

Peripheral Bus将外设(UART、GPIO)映射到固定内存地址。 - 开发者直接读写特定地址即可配置设备参数。

消费电子与PC

- GPU显存管理:独立显卡的显存通常映射到系统内存的高端地址(如

0xF0000000)。 - PCIe设备配置:PCI Express设备通过

BAR(Base Address Register)声明其寄存器在内存中的映射位置。

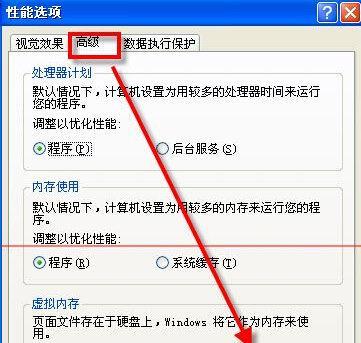

操作系统内核

操作系统内核通过MMIO与硬件交互:

- Linux内核使用

ioremap()函数将物理设备地址映射到虚拟地址空间。 - Windows中的

MmMapIoSpace实现类似功能。

存储器映射I/O的现代演进

随着计算机架构的发展,MMIO面临新的挑战和优化方向:

异构计算的影响

GPU和AI加速器可能通过统一虚拟地址空间(如NVIDIA的UVA)与CPU共享MMIO映射,减少数据拷贝开销。虚拟化技术的适配

在虚拟化环境中(如KVM、VMware),Hypervisor需模拟MMIO操作,将客户机的内存访问重定向到物理设备。内存计算(In-Memory Computing)

新型存储级内存(如Intel Optane)模糊了内存与存储界限,MMIO可能进一步与持久化内存(PMEM)技术结合。CXL协议的集成

Compute Express Link(CXL)协议支持设备通过缓存一致性协议共享内存,未来MMIO可能深度整合此类技术。

存储器映射I/O与端口映射I/O的对比

| 特性 | 存储器映射I/O(MMIO) | 端口映射I/O(PMIO) |

|---|---|---|

| 指令集 | 通用内存读写指令 | 专用I/O指令(如IN/OUT) |

| 地址空间 | 共享内存地址空间 | 独立I/O地址空间 |

| 性能 | 依赖内存总线带宽 | 可能受限于I/O总线 |

| 典型架构 | ARM、x86(部分设备) | x86传统外设(如早期PIC) |

存储器映射I/O通过统一内存与设备的访问方式,降低了硬件控制的复杂性,成为现代计算机系统的基石技术之一,尽管面临缓存一致性、安全性等挑战,但随着异构计算和新型总线协议的普及,MMIO将继续在高效硬件交互中发挥关键作用。

参考资料

- Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3.

- ARM Cortex-M4 Technical Reference Manual.

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy).

- PCI Express® Base Specification Revision 6.0.

— 结束**