反复刷新的存储器

- 行业动态

- 2025-05-03

- 5

动态随机存储器(DRAM)需周期性刷新以维持电容电荷,因存储单元通过栅极电容暂存数据,电荷会逐渐泄漏,静态存储器(SRAM)基于晶体管触发

反复刷新的存储器:动态随机存取存储器(DRAM)的深度解析

核心概念与特性

动态随机存取存储器(Dynamic Random-Access Memory, DRAM)是一种基于电容存储电荷原理的易失性存储器,其核心特点是需要周期性刷新以维持数据,这是因为电容会因漏电逐渐丢失电荷,以下是DRAM的关键特性:

- 易失性:断电后数据立即丢失。

- 高集成度:单个存储单元仅需一个电容和一个晶体管(1T1C结构),适合大容量存储。

- 低成本:相比静态RAM(SRAM),单位存储成本更低。

- 刷新依赖:必须通过外部电路定期刷新(通常每64毫秒)。

物理结构与工作原理

DRAM的存储单元由电容和访问晶体管组成,并通过行、列地址线实现矩阵化排列,以下是其核心组件与工作流程:

| 组件 | 功能描述 |

|---|---|

| 存储电容 | 存储二进制数据(充电为1,放电为0)。 |

| 行选通器(Row Decoder) | 根据行地址选择目标行,激活对应的字线(Word Line)。 |

| 列选通器(Column Decoder) | 根据列地址选择目标列,通过感放放大器(Sense Amplifier)读取或写入数据。 |

| 刷新控制器 | 定期触发刷新操作,恢复电容电荷。 |

工作流程示例:

- 行激活:行地址被解码后,目标行的字线通电,所有该行的电容与行选通器连接。

- 列操作:列地址选中特定电容,感放放大器检测电荷量并转换为逻辑值(0或1)。

- 数据刷新:刷新时,感放放大器读取所有行的数据并重新写入,补偿电容漏电。

刷新机制详解

DRAM的刷新分为两种模式:

| 刷新类型 | 触发条件 | 操作方式 |

|————–|—————————-|——————————————————————————|

| 分布式刷新 | 系统定时触发(如64ms周期) | 逐行刷新,每次刷新一行,避免集中操作导致性能下降。 |

| 自刷新(Self Refresh) | 进入省电模式(如休眠) | 利用存储单元自身的电容特性维持数据,减少刷新频率以降低功耗。 |

为何需要刷新:

电容存在漏电现象,典型情况下,电荷仅能维持约64毫秒,若不刷新,数据会在几秒内完全丢失。

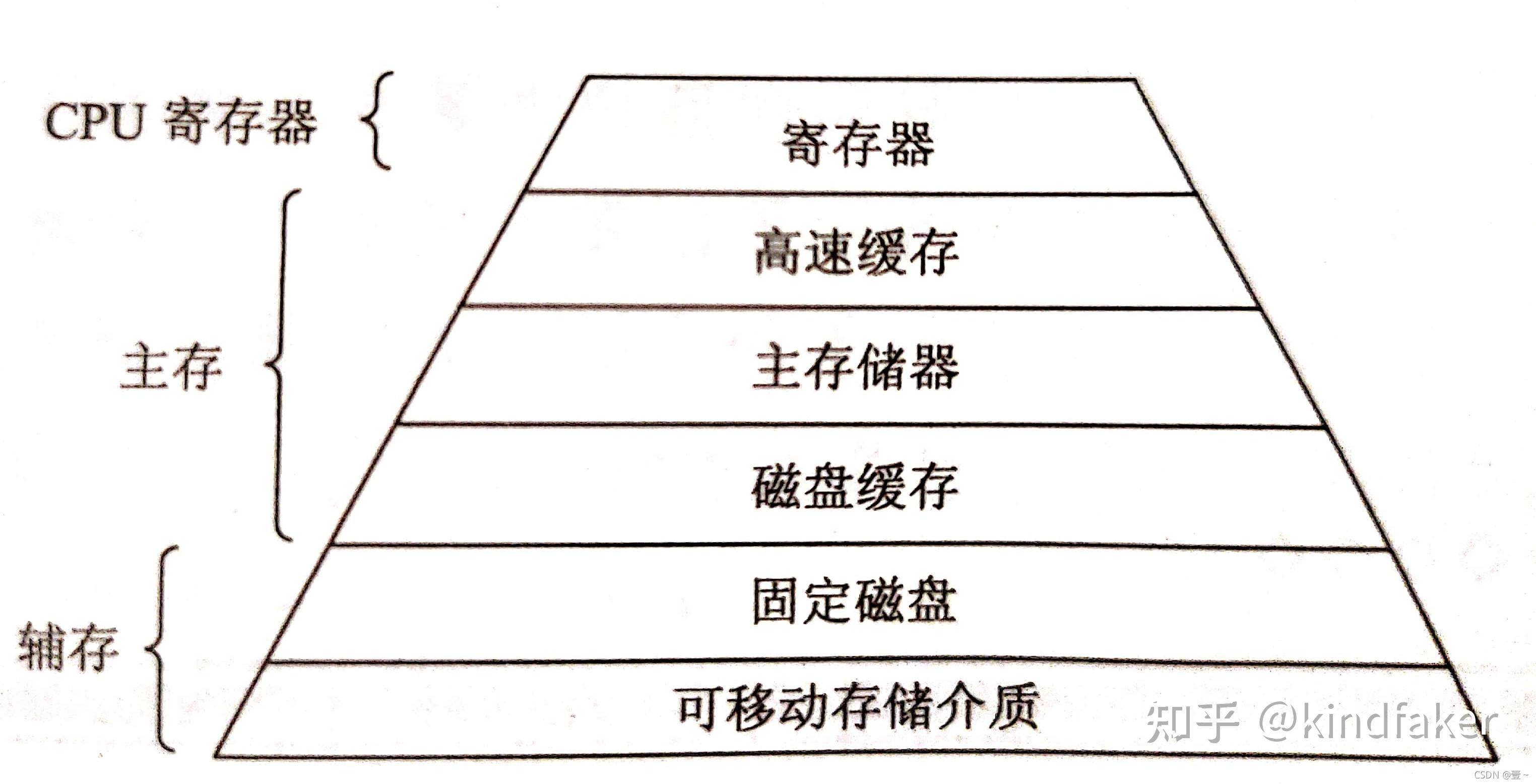

DRAM vs. 其他存储器

| 特性 | DRAM | SRAM | ROM/Flash |

|---|---|---|---|

| 刷新需求 | 必须周期性刷新 | 无需刷新 | 无需(ROM)或低频率(Flash) |

| 存储密度 | 高(适合大容量) | 低(高速缓存) | 中低(代码存储) |

| 速度 | 较慢(纳秒级延迟) | 快(亚纳秒级) | 慢(微秒级) |

| 成本 | 低(单位比特成本低) | 高 | 中高(取决于类型) |

| 易失性 | 是 | 是 | 否(ROM)/部分(Flash) |

应用场景与技术挑战

典型用途:

- 计算机主内存(如DDR4/DDR5内存条)

- 显卡显存(GDDR系列)

- 移动设备内存(LPDDR)

技术挑战:

- 刷新开销:频繁刷新消耗带宽和功耗,尤其在高性能计算中可能成为瓶颈。

- 缩放极限:随着制程缩小,电容漏电问题加剧,需改进材料(如铪基电容器)或架构(如3D堆叠)。

- 替代技术竞争:新兴存储器(如MRAM、ReRAM)试图以非易失性特性取代DRAM。

未来发展趋势

| 方向 | 技术进展 |

|---|---|

| 制程优化 | 采用EUV光刻提升密度,降低漏电。 |

| 新型材料 | 铪锆氧化物(HfO₂)提高电容稳定性。 |

| 混合存储架构 | 结合DRAM与非易失性存储器(如Optane)分层设计。 |

| 低功耗设计 | 改进自刷新算法,降低待机能耗。 |

FAQs

Q1:为什么DRAM需要刷新,而SRAM不需要?

A1:DRAM依赖电容存储电荷,而电容存在漏电问题,电荷会逐渐消失,因此必须周期性刷新以维持数据,SRAM则通过触发器(Flip-Flop)电路存储数据,只要供电正常即可持续保持状态,无需刷新。

Q2:DRAM的刷新频率可以调整吗?会影响性能吗?

A2:刷新频率通常由硬件设定(如每64ms),但部分系统允许通过BIOS或软件延长刷新间隔以降低功耗,过度延长会导致数据错误风险增加,频繁刷新会占用内存带宽,可能影响突发读写性能,因此现代内存控制器会优化刷新时机(如空闲