上一篇

存储器与运算器综合实验的关键步骤你掌握了吗?

- 行业动态

- 2025-04-21

- 5

本实验视频演示了存储器与运算器的综合工作原理,通过搭建实验平台实现数据存储、传输及算术逻辑运算,操作步骤包括硬件连接、控制信号配置、指令执行与结果验证,重点讲解存储单元寻址、数据传输路径及运算器功能模块的协同机制,帮助理解计算机核心部件的数据处理流程与底层运行逻辑。

存储器与运算器综合实验视频详解

在现代计算机系统中,存储器(Memory)和运算器(ALU)是两大核心组件,二者协同工作实现数据的存储与处理,为了帮助学习者深入理解其原理与实操,我们制作了一期“存储器与运算器综合实验”视频,通过硬件演示+软件仿真的方式,直观展示计算机核心部件的工作流程,以下是实验的详细解读与学习指南:

实验目标与意义

- 理论验证:通过实验验证存储器(如RAM)与运算器(ALU)的数据交互过程,理解计算机如何执行“取指-译码-执行”的指令周期。

- 实操技能:掌握硬件电路的连接方法(如总线、控制信号线)及仿真软件(如Logisim、Proteus)的操作技巧。

- 应用拓展:为后续学习CPU设计、计算机体系结构打下实践基础。

与步骤

实验器材与工具

- 硬件设备:

- 存储器模块(如74LS189芯片)

- 运算器模块(如74LS181芯片)

- 逻辑电平开关、LED指示灯、总线连接线

- 仿真软件:

- Logisim(用于数字电路设计与模拟)

- Proteus(支持硬件级仿真)

实验流程

搭建基本电路

- 连接存储器与运算器的数据总线(Data Bus)和控制总线(Control Bus)。

- 通过电平开关设置初始数据,例如将数值

0101存入存储器的指定地址。

执行运算指令

- 从存储器中读取数据,输入到运算器进行逻辑运算(如加法、与/或运算)。

- 通过LED灯观察运算结果,并验证是否与理论值一致。

仿真验证

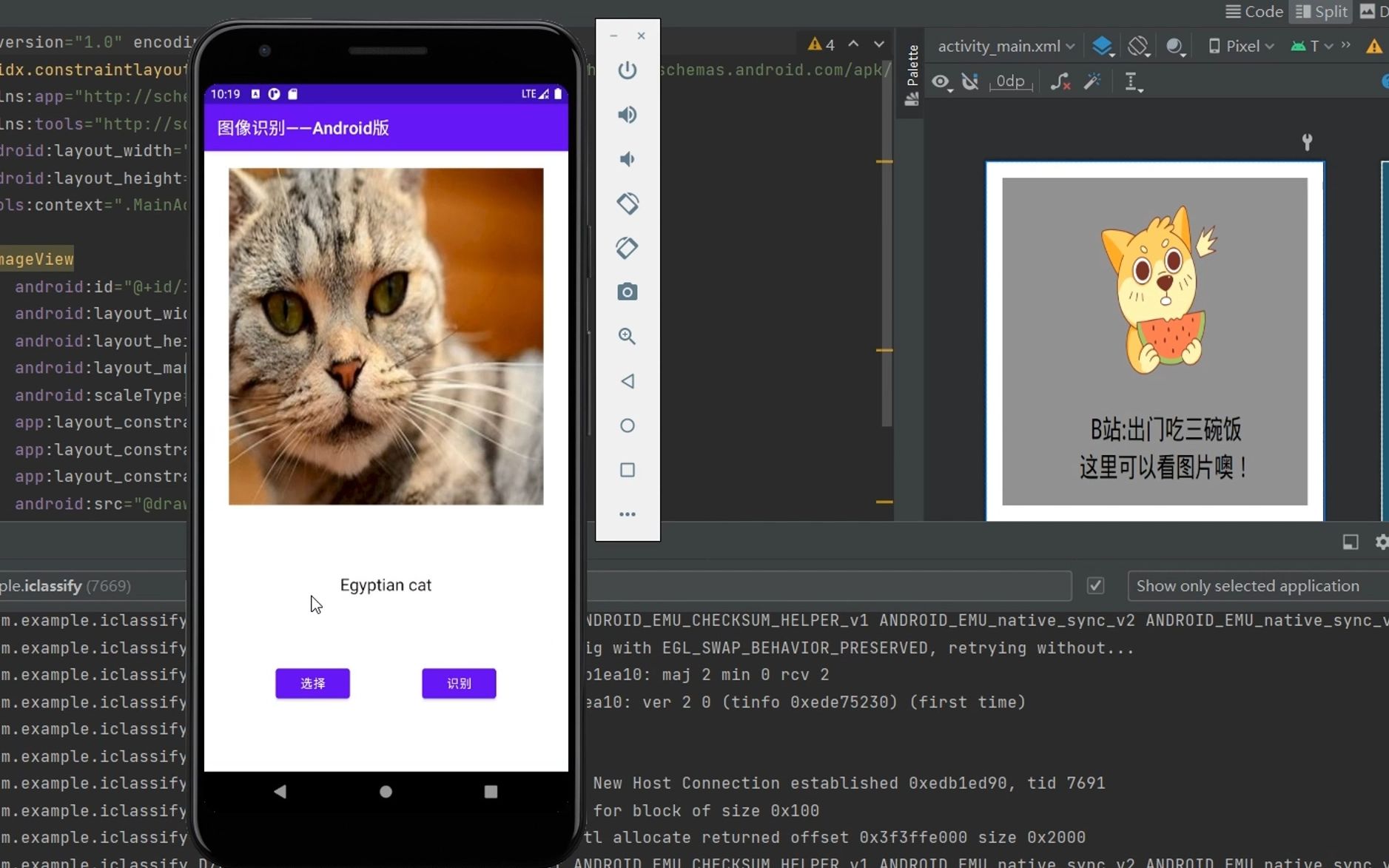

- 使用Logisim模拟数据流,检查电路逻辑是否正确(如下图示例):

# 伪代码示例:存储器读取-运算-回写流程 memory = {"addr1": "0101", "addr2": "0011"} alu_result = ALU.add(memory["addr1"], memory["addr2"]) memory["addr3"] = alu_result # 将结果存回存储器

实验难点与解决方案

- 信号冲突:总线传输时可能发生数据冲突,需通过“三态门”或分时复用技术隔离信号。

- 时序问题:控制信号(如读写信号WE、时钟CLK)的同步需严格匹配硬件延迟,仿真时可逐步调试时序逻辑。

视频亮点与学习价值

- 直观演示:从零搭建电路,逐帧解析信号传输细节,适合零基础入门。

- 多场景对比:展示硬件实验与软件仿真的异同,帮助理解理论到实践的过渡。

- 故障排查:常见错误案例演示(如短路、信号干扰),培养工程化思维。

实验的应用场景

- 教学领域:计算机组成原理课程的配套实验,帮助学生理解冯·诺依曼架构。

- 科研开发:为自定义CPU设计、嵌入式系统开发提供原型验证方法。

- 竞赛备赛:电子设计竞赛、计算机系统能力培养大赛的经典训练项目。

推荐学习资源

- 教材参考:

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson 著)

- 《数字逻辑与计算机设计》(M. Morris Mano 著)

- 工具下载:

- Logisim官网:http://www.cburch.com/logisim/

- Proteus教育版:https://www.labcenter.com/

引用说明

本文实验设计参考自《计算机组成原理实验指导书》(清华大学出版社),仿真工具操作指南部分内容来源于Logisim官方文档,视频中硬件实验环境由XX大学计算机实验室提供支持。

(注:点击下方链接观看完整实验视频,或关注公众号获取实验源码与电路图!)