如何高效分析存储器电路的关键问题?

- 行业动态

- 2025-04-19

- 7

存储器是电子设备的核心组件之一,其电路设计直接影响设备的性能、功耗和可靠性,本文从技术原理、电路结构及关键参数入手,深入解析存储器的工作原理与实现方式。

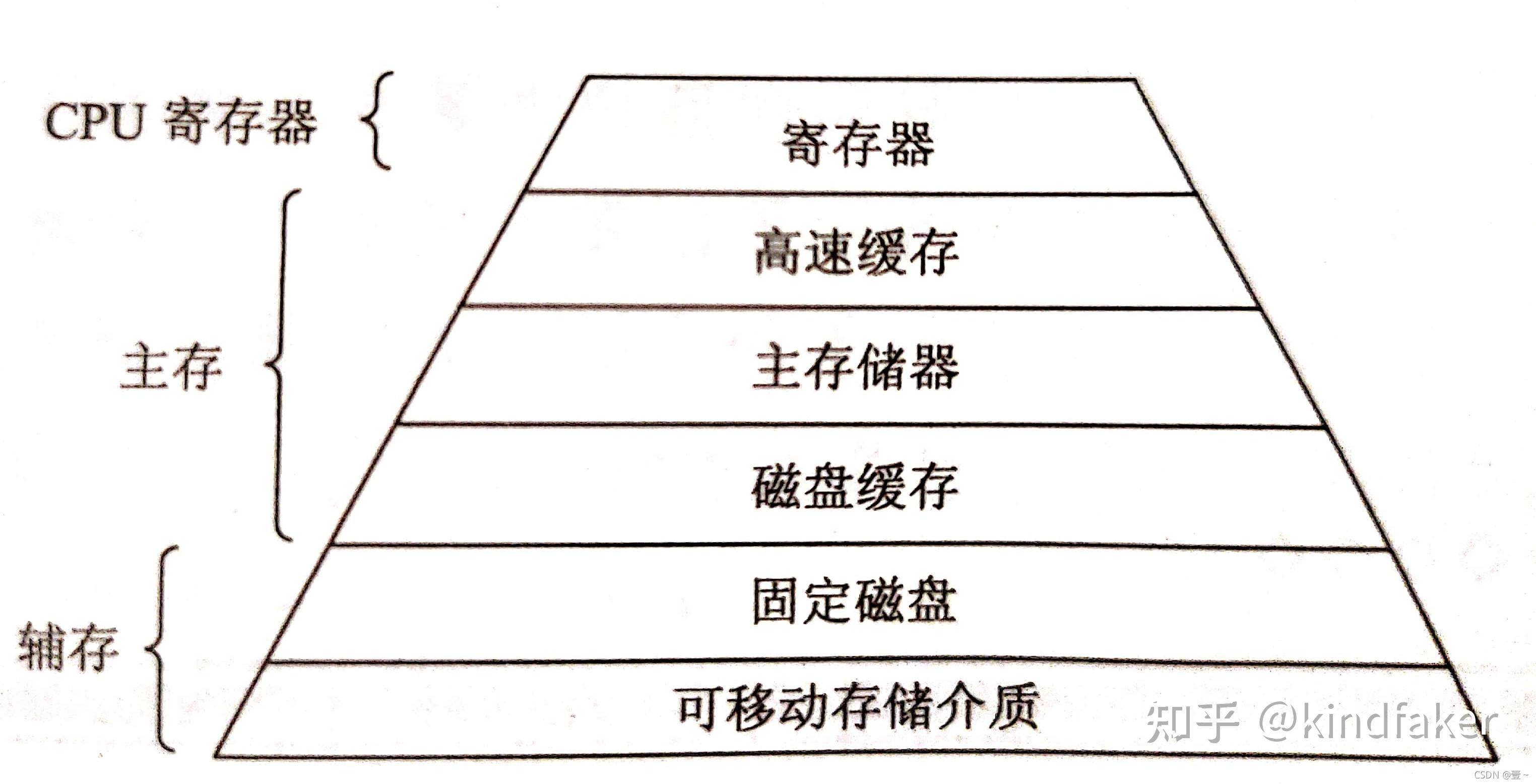

存储器的分类与技术特性

按存储介质划分

- 半导体存储器:DRAM、SRAM、Flash(NAND/NOR)

- 磁性存储器:硬盘(HDD)、磁带

- 光学存储器:CD、DVD、蓝光

按访问特性划分

- 随机访问存储器(RAM):DRAM(动态)需定期刷新,SRAM(静态)无需刷新但成本高

- 只读存储器(ROM):PROM、EPROM、EEPROM支持不同编程方式

- 非易失性存储器:Flash通过浮栅晶体管保存电荷,断电后数据不丢失

核心电路结构分析

存储单元电路

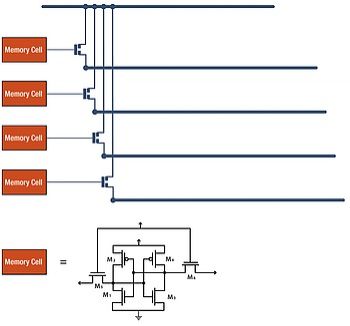

SRAM单元(6T结构)

由两个交叉耦合的反相器(4个MOS管)和两个存取晶体管(NMOS)构成。

优势:读写速度快(1-10ns),无刷新需求。

缺点:占用面积大,功耗较高。DRAM单元(1T1C结构)

单个MOS管与电容组成,通过电容电荷存储数据(0/1)。

刷新机制:每64ms通过行地址选通刷新电荷。

电路挑战:电容漏电导致数据丢失,需复杂外围电路支持。NAND Flash单元

浮栅晶体管通过Fowler-Nordheim隧穿或热电子注入写入数据。

页式读写:以页(4KB)为单位操作,擦除以块(256KB-4MB)为单位。

外围控制电路

地址译码器

将二进制地址转换为物理存储单元的选通信号,分列译码与行译码两级结构。读写放大器(Sense Amplifier)

关键电路模块,检测存储单元微小电压差(DRAM约200mV),放大至逻辑电平。预充电电路

在DRAM读写前对位线预充电至Vdd/2,提升信号灵敏度。

存储器读写流程与信号时序

SRAM写入过程

- 字线(WL)置高电平,开启存取晶体管

- 位线(BL)与互补位线(BLB)分别驱动高低电平,强制反相器状态翻转

DRAM读取流程

- 预充电位线至中间电压

- 行地址选通,单元电容电荷与位线共享

- 读写放大器检测电压差并放大输出

NAND Flash编程

- 选定页内所有单元浮栅同时充电

- 施加高压(~20V)使电子隧穿进入浮栅

- 验证阶段检测阈值电压是否达到目标值

关键性能参数与优化方向

延迟参数

- tRCD(行选通到列选通延迟):DRAM典型值12-18ns

- tWR(写恢复时间):SRAM约1-2个时钟周期

带宽计算

DDR4-3200理论带宽=3200MHz×64bit×2(双倍速率)=51.2GB/s功耗优化技术

- 低电压设计:LPDDR5工作电压降至1.05V

- 门控时钟:关闭空闲存储体的时钟信号

- 多Bank并行操作降低激活功耗

应用场景与选型建议

- 嵌入式系统:NOR Flash用于代码存储(XIP特性)

- 服务器内存:LRDIMM DDR5支持TB级容量扩展

- 移动设备:UFS 4.0采用M-PHY 4.1接口,速度达4.2GB/s

- 工业控制:FRAM(铁电存储器)抗辐射且耐高低温

可靠性设计与故障防护

纠错编码(ECC)

采用汉明码或BCH码纠正单比特/多比特错误,DRAM模块标配ECC功能。磨损均衡算法

SSD控制器通过动态映射表分散NAND块擦写次数。温度补偿电路

动态调整刷新频率(DRAM温度每升高10°C,刷新速率需提升2倍)。

引用说明

本文技术细节参考《数字电子技术基础》(阎石著)、美光科技《DRAM系统架构白皮书》、IEEE固态电路期刊(JSSC)相关论文,以及Intel《3D NAND技术演进报告》。