上一篇

存储器结构如何决定数据存取速度?

- 行业动态

- 2025-04-20

- 6

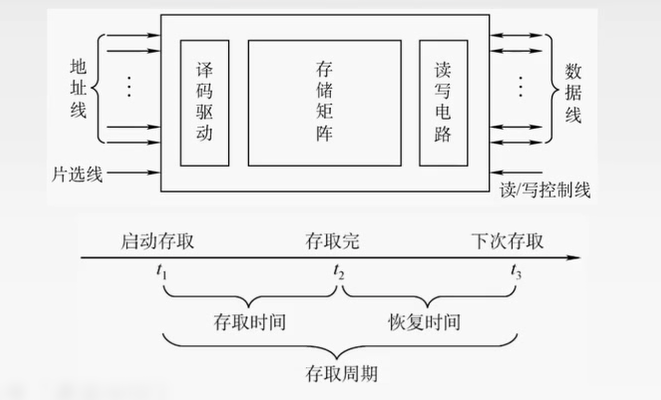

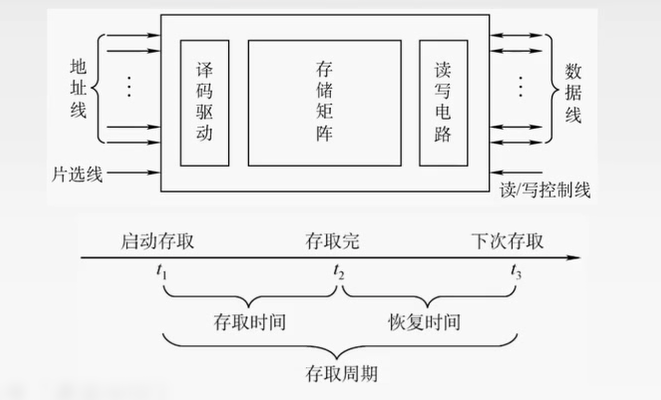

存储器通过逻辑电路分层存储数据,分为易失性与非易失性两类,其结构包含地址译码、读写控制等模块,采用缓存-主存-外存多级体系平衡速度与容量,数据通过总线传输,依靠单元阵列和时序电路实现寻址与存取,需满足稳定性、密度及功耗等技术指标。

存储器层级体系:速度与容量的平衡

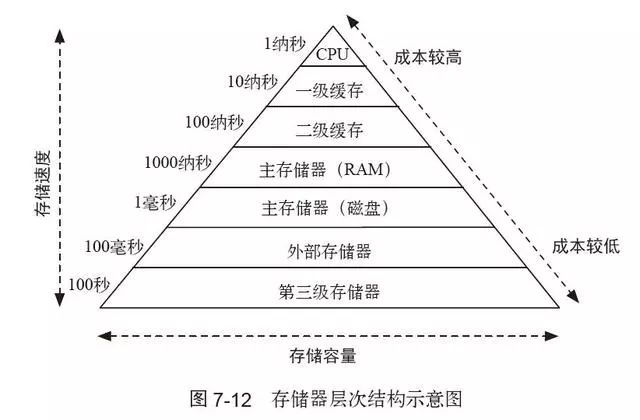

计算机采用多级存储架构以兼顾速度与成本:

- 寄存器(CPU内部)

- 访问延迟:0.1-1纳秒

- 容量:几十至几百字节

- 直接参与CPU运算,采用SRAM技术

- 高速缓存(Cache)

- L1/L2/L3三级设计

- 访问延迟:1-10纳秒

- 容量:KB到MB级

- 通过空间局部性、时间局部性提升命中率

- 主存储器(内存)

- 访问延迟:50-100纳秒

- 容量:GB级

- DRAM技术,需周期性刷新保持数据

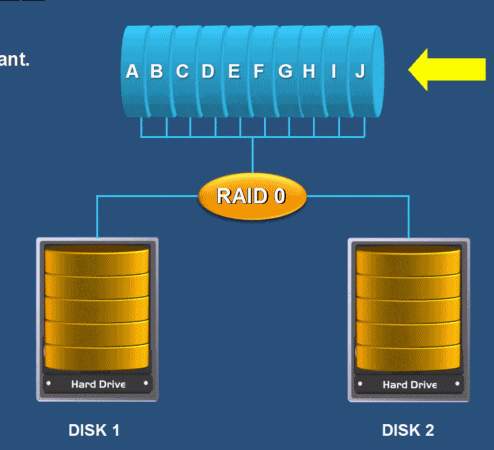

- 辅助存储器(硬盘/SSD)

- 访问延迟:毫秒级

- 容量:TB级

- 非易失存储,含机械硬盘(HDD)与固态硬盘(SSD)

(配图说明:典型存储层级的速度-容量关系)

核心物理结构解析

DRAM单元结构

- 存储单元:由1个晶体管+1个电容构成

- 数据保存:电容电荷表示0/1,需每64ms刷新一次

- 寻址方式:行地址选通(RAS)与列地址选通(CAS)

NAND闪存架构

- 基本单元:浮栅MOS管

- 存储原理:通过隧穿效应注入/释放电荷

- 组织方式:页(4KB-16KB)→块(128-256页)→面→芯片

3D堆叠技术

- 垂直堆叠:将存储单元立体排布(如三星V-NAND)

- 优势:单位面积容量提升5-10倍,功耗降低40%

寻址与访问机制

内存映射原理

- 线性地址→物理地址:通过MMU完成虚拟地址转换

- Bank分组:DRAM芯片划分多个bank实现并行访问

缓存关联性

| 关联方式 | 特点 | 应用场景 |

|---|---|---|

| 直接映射 | 固定地址映射,易冲突 | 低功耗设备 |

| 全相联映射 | 任意位置存储,命中率高 | 高端CPU L1缓存 |

| 组相联映射 | 折中方案(如4-way/8-way) | 主流CPU L2/L3缓存 |

SSD磨损均衡

- 动态映射表:FTL控制器动态分配物理块

- 算法类型:动态磨损均衡(DWL)、静态磨损均衡(SWL)

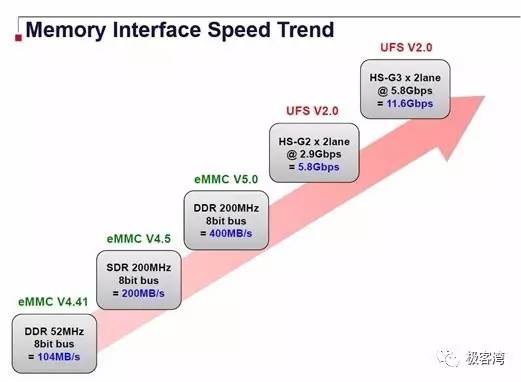

关键技术演进

- HBM(高带宽内存)

通过硅通孔(TSV)堆叠芯片,带宽达512GB/s - PCM相变存储器

利用硫族化合物晶态/非晶态变化存储数据 - Optane持久内存

基于3D XPoint技术,兼具DRAM速度与SSD非易失性

存储器分类图谱

按存取方式: ┌─随机存取(RAM/ROM) ├─顺序存取(磁带) └─直接存取(硬盘) 按易失性: ├─易失存储器(DRAM/SRAM) └─非易失存储器(NAND/3D XPoint) 按功能: ├─主存(运行存储) ├─缓存(加速访问) └─外存(长期存储)

典型应用场景

- 边缘计算设备:采用MRAM实现低功耗即时存储

- AI训练集群:HBM+NVMe SSD构建分级存储体系

- 物联网终端:NOR Flash存储固件程序

常见问题

Q:为什么内存需要不断刷新?

A:DRAM电容电荷会自然泄漏,周期性刷新(通常64ms)可维持数据完整性。

Q:SSD寿命由什么决定?

A:主要取决于闪存类型(SLC/MLC/TLC)和写入放大系数(WA),高端企业级SSD可达10 DWPD(每日全盘写入次数)。

Q:L1缓存为什么比主存快千倍?

A:L1集成在CPU内核旁,采用高速SRAM且总线位宽达512bit,而主存需通过内存控制器访问。

引用说明

- 存储器基础理论:《计算机组成与设计》(David Patterson, John Hennessy)

- DRAM技术标准:JEDEC JESD79-4B

- 3D NAND演进:三星电子《V-NAND技术白皮书》

- 新型存储器研究:IEEE Transactions on Electron Devices