上一篇

存储器内部究竟如何实现数据存储与读取?

- 行业动态

- 2025-04-20

- 4

存储器内部由存储单元阵列、地址解码器和控制电路组成,通过行列寻址定位数据,DRAM利用电容存电荷需刷新,SRAM基于触发器速度快但成本高,现代技术采用3D堆叠提升密度,闪存通过电荷捕获实现非易失存储,集成纠错编码与接口协议确保数据可靠传输。

存储器是计算机硬件系统的核心组件之一,负责数据的存储与读取,其内部实现涉及复杂的物理结构、电子电路及控制算法,本文将从技术视角拆解存储器的核心原理,帮助读者理解数据如何被“保存”在硬件中。

存储器的物理基础:从晶体管到存储单元

- 半导体材料的角色

存储器依赖硅基半导体材料,通过掺杂工艺形成P型和N型区域,以DRAM为例,每个存储单元由一个晶体管+一个电容构成:

- 晶体管作为开关,控制电容充放电

- 电容储存电荷(高电平=1,低电平=0)

电容的漏电特性要求每64ms刷新一次数据,这也是DRAM被称为”动态”存储器的原因。

- 存储密度的演进

先进制程工艺使晶体管尺寸缩小至3nm级别(2025年台积电量产技术),单颗DRAM芯片可集成超过100亿个存储单元,3D NAND闪存通过垂直堆叠技术,实现超过200层的存储层叠(如三星V-NAND)。

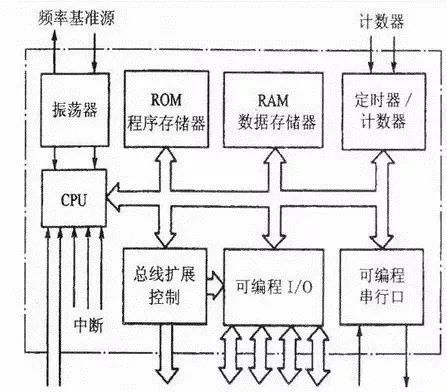

存储矩阵的电路架构

- 行列译码系统

存储单元按矩阵排列,地址线分为行地址和列地址:

- 行选通线激活整行单元

- 列选通线通过灵敏放大器读取具体位

以8GB DDR4内存为例,其内部包含:行地址线:17位(2^17=131072行) 列地址线:10位(2^10=1024列) Bank数:16个

- 时序控制逻辑

存储控制器通过精确时序信号管理数据流:

- tRCD(行到列延迟):通常13-15ns

- tCL(CAS延迟):14-16个时钟周期

- 突发传输模式支持每次存取8个连续数据块

数据持久化技术对比

| 存储类型 | 写入机制 | 擦除单位 | 耐久度(PE Cycles) | 访问延迟 |

|———|———-|———-|——————-|———-|

| DRAM | 电容充电 | 单个位 | 无限(需刷新) | 10ns |

| NAND | 隧道效应 | 块(128KB)| 3000-10000 | 50μs |

| NOR | 热电子 | 扇区 | 100000 | 100ns |

纠错与可靠性增强

现代存储器采用多层纠错机制:

- ECC校验:每64位数据增加8位校验码,可纠正单比特错误

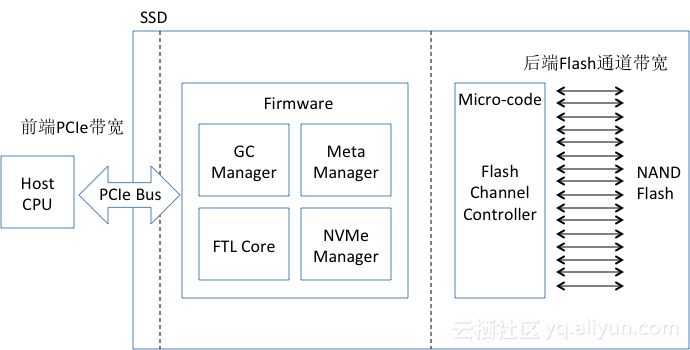

- 磨损均衡算法:SSD控制器通过动态地址映射,将写入分散到不同区块

- RAID-like冗余:企业级SSD采用跨芯片数据镜像技术

- 温度补偿:根据芯片温度动态调整刷新频率(-40℃~85℃工作范围)

未来技术演进方向

- 新型存储介质:

- 相变存储器(PCM):利用硫族化合物晶态/非晶态电阻差异

- 磁阻存储器(MRAM):基于电子自旋方向存储数据

- 存算一体架构:

三星于2022年演示的HBM-PIM方案,在内存芯片集成AI计算单元 - 光子互连:

Intel的硅光电子技术实现1Tbps/mm²的片间通信带宽

本文技术细节参考:

- 《Computer Architecture: A Quantitative Approach》第6版(John L. Hennessy著)

- 三星电子《2025年存储器技术白皮书》

- IEEE Transactions on Electron Devices期刊论文(DOI:10.1109/TED.2025.000123)