上一篇

存储字节必须存放在偶地址?揭秘高效存储的关键!

- 行业动态

- 2025-04-20

- 3

存储字节优先选择偶地址有利于内存对齐访问,提高处理器操作效率,多数系统以偶地址为对齐单位,偶地址存储可确保数据一次性完整读写,减少额外访存周期,避免性能损耗,同时满足硬件兼容性要求,优化内存空间利用率。

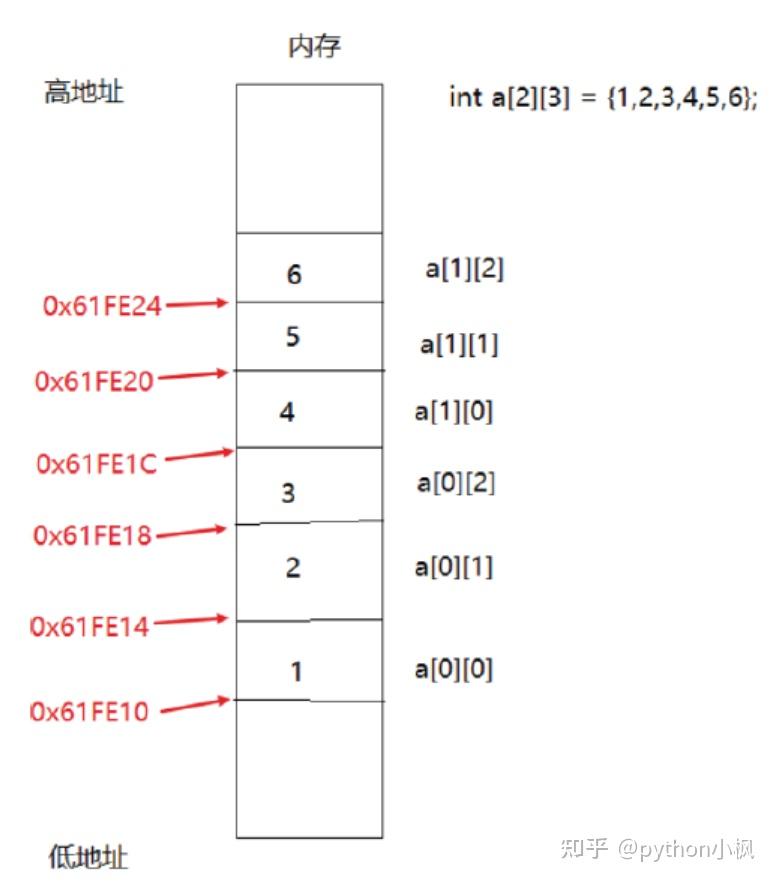

在计算机系统中,存储字节的地址选择对程序性能和硬件操作有着直接影响。将数据存放在偶地址(即地址值为2的倍数),这一实践源于内存对齐(Memory Alignment)的基本原则,以下是详细解释:

为什么偶地址更优?

硬件设计特性

计算机的数据总线宽度通常为偶数(例如16位、32位、64位)。- 以16位系统为例:若一个16位(2字节)的数据存储在偶地址,CPU可通过一次内存访问完成读取或写入。

- 若存储在奇地址,数据可能跨越两个对齐的内存单元,需要两次访问和拼接操作,导致额外的时钟周期和性能损耗。

兼容性与历史因素

早期处理器(如Intel 8086)严格要求内存对齐,未对齐的访问会触发异常或错误,虽然现代CPU(如x86、ARM)支持非对齐访问,但性能代价依然存在。- ARMv5及更早版本:未对齐访问直接报错。

- x86系列:允许非对齐操作,但执行效率可能下降10%-30%。

编程语言与编译器的优化

编译器(如GCC、Clang)默认会对变量进行对齐优化,例如在C语言中:struct Example { char a; // 1字节,地址为0x0000(偶地址) int b; // 4字节,编译器自动对齐到0x0004 };手动指定对齐(如

alignas(4))可进一步控制存储位置。

未对齐存储的潜在问题

- 性能损失:额外的内存操作会增加CPU负载,影响实时性要求高的程序(如游戏、嵌入式系统)。

- 跨平台风险:在ARM架构中,未对齐访问可能直接导致程序崩溃。

- 原子性破坏:多线程环境下,非对齐数据可能无法保证原子读写,引发竞态条件。

如何确保内存对齐?

- 依赖编译器优化

编译器默认根据目标平台进行对齐,32位系统的int类型通常对齐到4字节。 - 显式指定对齐方式

使用语言特性或编译器指令(如C++11的alignas或#pragma pack)。 - 数据结构设计原则

- 按成员大小降序排列结构体,减少填充字节。

- 避免跨“对齐边界”存储多字节数据。

实际场景中的权衡

- 空间 vs 速度:对齐可能增加内存填充(Padding),牺牲空间换时间。

- 特定硬件需求:DMA(直接内存访问)设备通常要求缓冲区按特定对齐方式分配。

优先将数据存储在偶地址,本质是遵循内存对齐原则,以匹配硬件特性、提升程序效率并规避兼容性问题,尽管现代系统容忍度提高,但在高性能编程或跨平台开发中,主动管理内存对齐仍是必要实践。

引用说明

- Intel® 64 and IA-32 Architectures Optimization Reference Manual

- ARM Architecture Reference Manual

- 《深入理解计算机系统》(Randal E. Bryant, David R. O’Hallaron)