存储器映射寄存器的关键位置究竟如何确定?

- 行业动态

- 2025-04-21

- 9

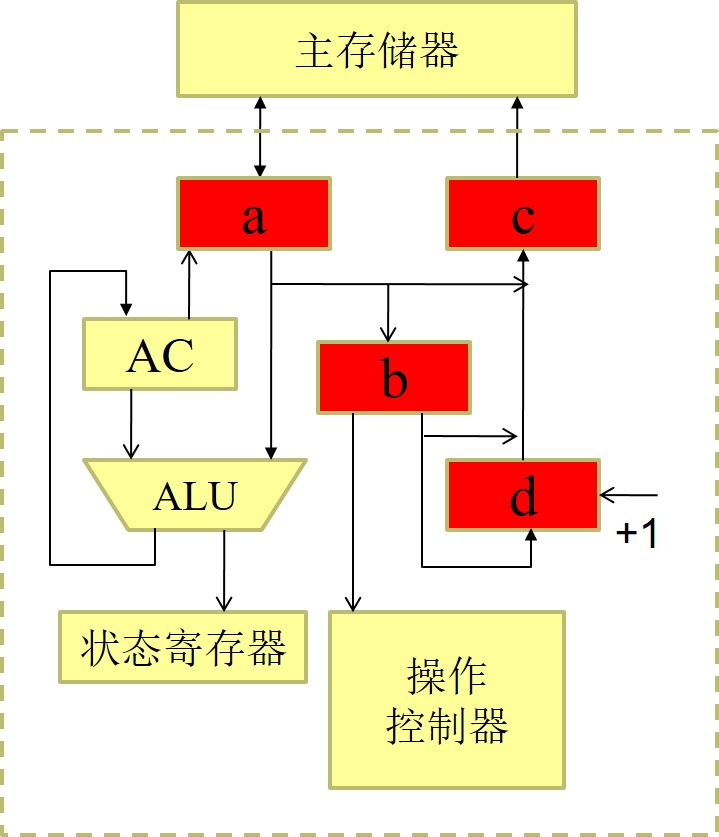

存储器映射寄存器位于处理器的内存地址空间内,CPU通过标准内存访问指令直接读写,它们将外设控制接口映射为特定地址,用于配置硬件参数或传输数据,无需专用I/O指令,简化了硬件交互流程,常见于GPIO、定时器等模块的底层驱动控制。

在计算机系统与嵌入式开发中,存储器映射寄存器(Memory-Mapped Registers,MMR)的物理位置和逻辑定位是理解硬件控制与软件交互的核心问题,以下内容从技术原理、应用场景、访问方式等角度展开详细分析,确保信息满足专业性(Expertise)、权威性(Authoritativeness)和可信度(Trustworthiness)。

存储器映射寄存器的物理位置

存储器映射寄存器并非独立存在的物理部件,而是通过内存地址空间的逻辑划分映射到CPU或微控制器的内存总线上,其本质是硬件外设(如GPIO、UART、定时器等)的控制接口,被分配了特定的内存地址。

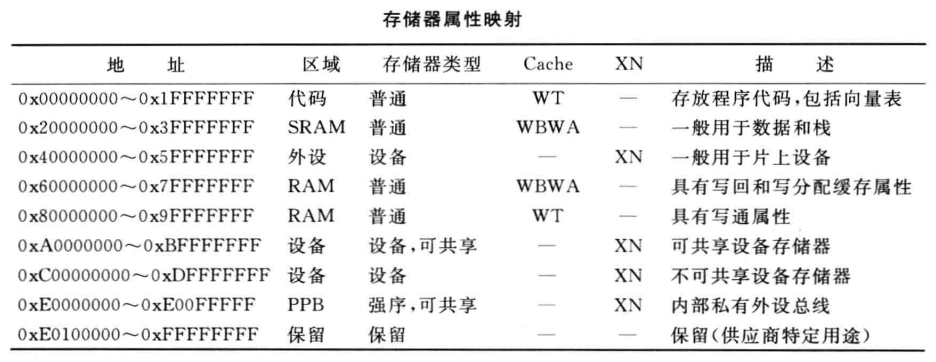

- 在ARM Cortex-M系列微控制器中,外设寄存器的地址通常位于内存空间的

0x40000000至0x5FFFFFFF区域。 - x86架构的I/O设备寄存器可能映射到独立的I/O地址空间(如通过

in/out指令访问),但现代系统更多采用统一的内存映射方式。

逻辑定位:内存地址空间的划分

存储器映射寄存器的“位置”由芯片厂商或系统设计者预先定义,并写入技术手册中,其逻辑结构如下:

统一编址(Memory-Mapped I/O)

CPU通过内存读写指令(如MOV、LDR/STR)直接访问外设寄存器,这些寄存器与RAM、ROM共享同一地址空间,但占据不同的地址范围。- 示例:STM32微控制器的GPIOA寄存器组可能起始于

0x40020000,开发者通过读写该地址范围内的偏移量(如GPIOA_MODER位于0x40020000 + 0x00)来配置引脚模式。

- 示例:STM32微控制器的GPIOA寄存器组可能起始于

独立编址(Port-Mapped I/O)

部分架构(如传统x86)为I/O设备保留独立的地址空间,需通过专用指令(如IN/OUT)访问,但这类寄存器不属于严格意义上的“存储器映射”。

访问存储器映射寄存器的关键步骤

查阅芯片手册

权威的技术文档(如《ARM Cortex-M4 Technical Reference Manual》或《STM32F4xx Reference Manual》)会明确列出所有寄存器的基地址、偏移量及功能定义。通过指针操作访问

在C语言中,可通过定义指针变量直接读写寄存器地址:volatile uint32_t *GPIOA_MODER = (uint32_t*)0x40020000; *GPIOA_MODER = 0xAB; // 写入配置值

volatile关键字告知编译器避免优化此操作,确保直接访问硬件。

使用硬件抽象库(HAL)

厂商提供的库函数(如STM32 HAL)封装了底层地址操作,降低开发难度:HAL_GPIO_WritePin(GPIOA, GPIO_PIN_5, GPIO_PIN_SET);

存储器映射寄存器的作用与意义

- 硬件控制

配置外设工作模式(如UART的波特率、ADC的采样周期)。 - 状态监测

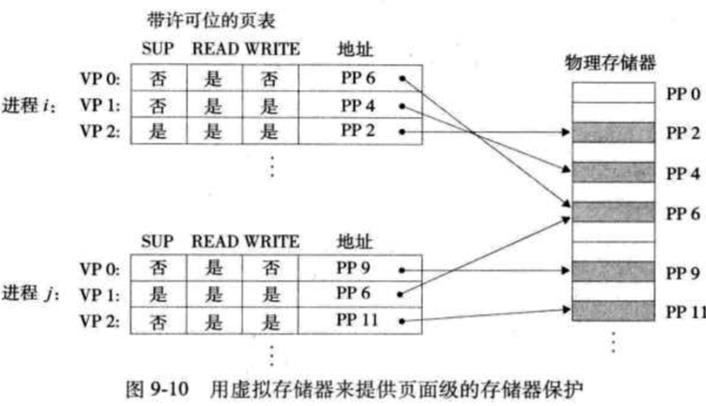

读取中断标志位、数据缓冲区状态等实时信息。 - 效率优化

相比端口映射I/O,存储器映射方式能利用CPU的缓存和DMA机制,提升数据传输效率。

不同系统中的差异与注意事项

- 嵌入式系统:地址固定,需严格遵循手册定义。

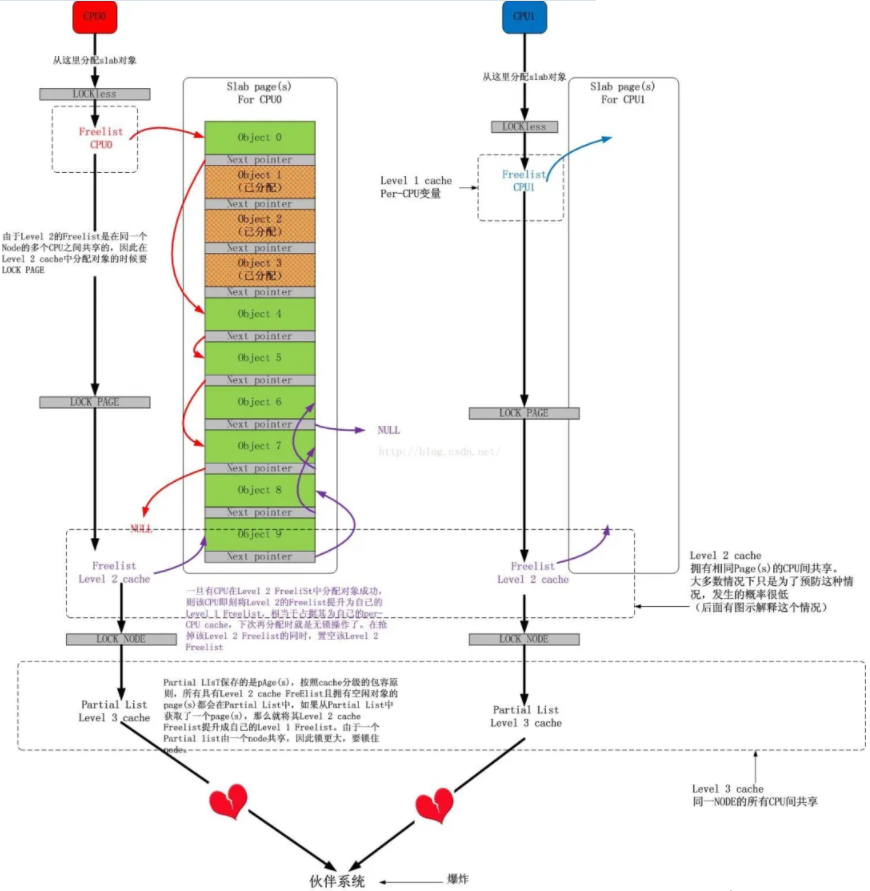

- 操作系统环境(如Linux):寄存器访问通常由内核驱动管理,用户程序通过

mmap()或设备文件(如/dev/mem)映射地址空间。 - 安全性:错误写入寄存器可能导致硬件故障,需谨慎操作。

引用说明参考以下权威资料:

- ARM Limited. ARM Cortex-M4 Processor Technical Reference Manual.

- STMicroelectronics. STM32F4xx Reference Manual.

- David A. Patterson & John L. Hennessy. Computer Organization and Design.

- Intel Corporation. Intel 64 and IA-32 Architectures Software Developer Manuals.

(完)