上一篇

存储器通常由存储矩阵

- 行业动态

- 2025-04-14

- 4

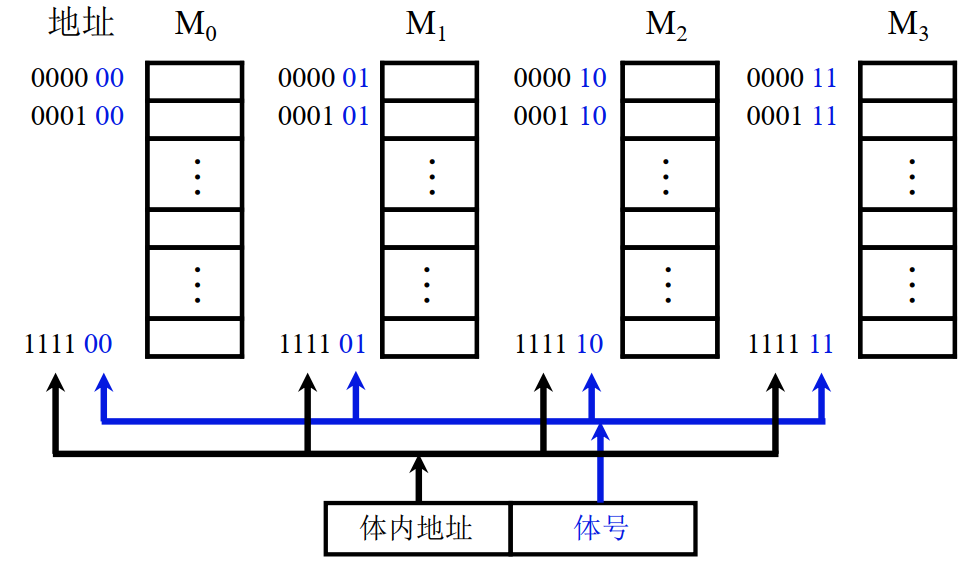

存储器通常由存储矩阵、地址译码器和控制电路组成,

存储矩阵为核心部分,由行列排布的存储单元构成,每个单元保存1位二进制数据,地址译码器通过行列选择线精确定位单元,控制电路协调读写操作,实现数据的高效存取与管理。

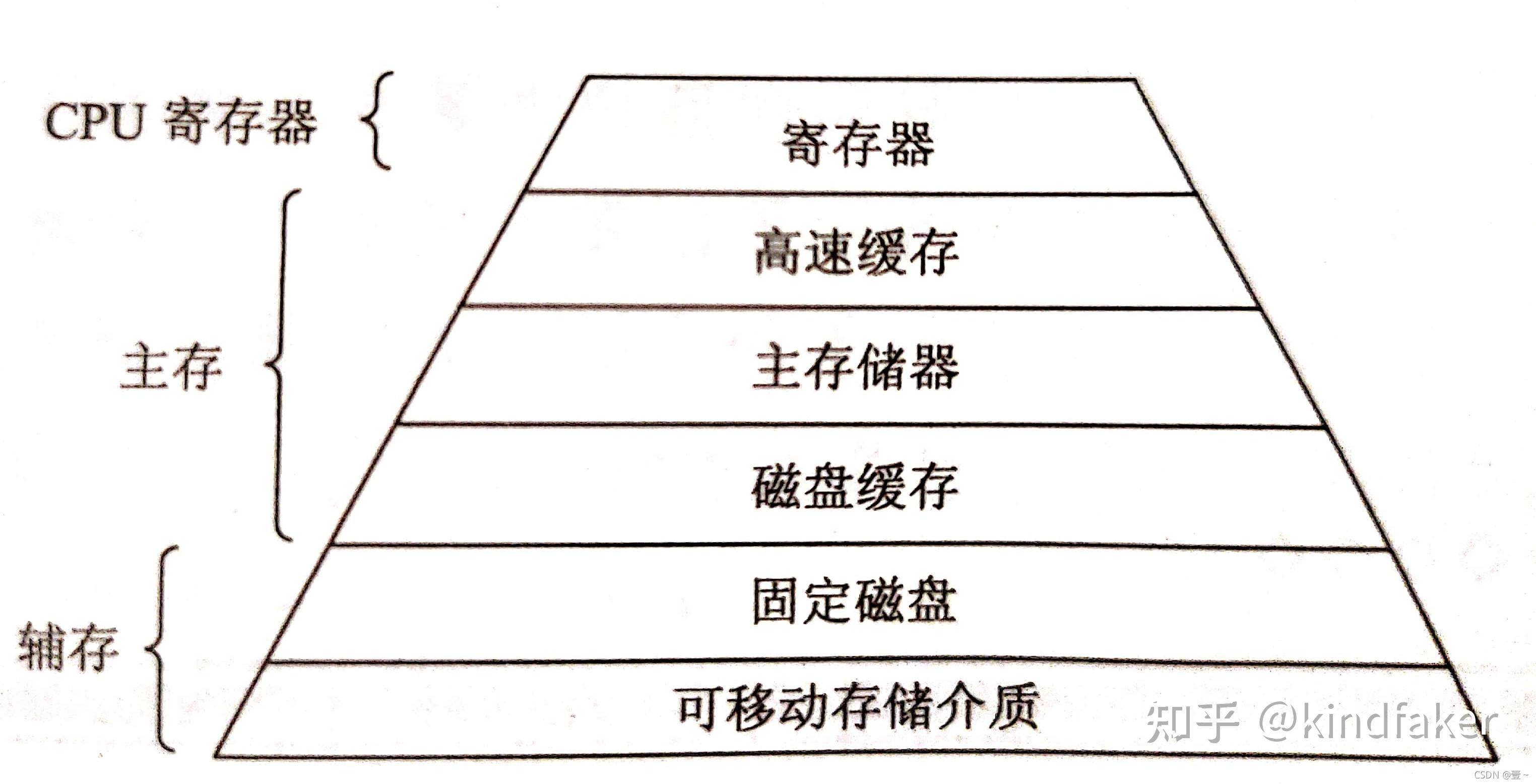

存储器是计算机系统中用于保存程序与数据的核心部件,其物理实现依赖于高度精密的电路结构,存储矩阵(Memory Array)作为存储器的核心组成部分,其设计直接影响存储容量、访问速度与功耗,以下从技术原理、结构组成及行业应用维度展开分析。

存储矩阵的物理结构与工作原理

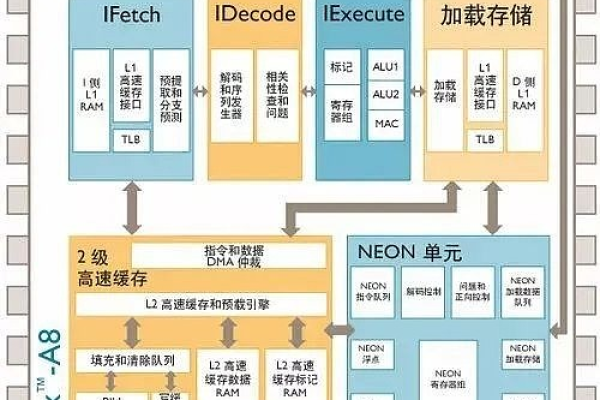

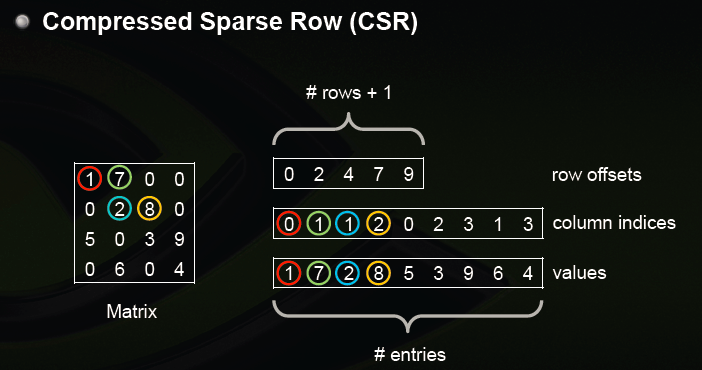

存储矩阵由规则排列的存储单元(Memory Cell)构成,每个单元通过唯一坐标(行地址与列地址)定位,以DRAM为例,单个存储单元包含一个晶体管与一个电容:晶体管作为开关控制数据存取,电容存储电荷状态(0或1),访问过程分为三个步骤:

- 行地址译码:输入的行地址经译码器激活对应字线(Word Line),选中整行单元。

- 电荷放大:被选行中所有单元电容的电荷通过位线(Bit Line)传输至灵敏放大器,将微弱电荷信号转换为标准逻辑电平。

- 列地址选择:列译码器根据列地址选择目标位线,完成数据读写操作。

存储矩阵的关键技术演进

- 单元微型化:通过光刻工艺升级,DRAM单元尺寸从90nm演进至10nm以下,单位面积存储密度提升超100倍。

- 3D堆叠技术:NAND闪存采用3D堆叠结构,如三星V-NAND通过垂直堆叠128层单元,实现单芯片1Tb容量(来源:IEEE ISSCC 2021)。

- 新型存储介质:相变存储器(PCM)利用硫族化合物晶态/非晶态电阻差异存储数据,读写速度可达纳秒级(IBM研究院数据)。

存储矩阵的电路辅助模块

- 纠错编码(ECC):采用汉明码或Reed-Solomon码检测并修正数据错误,将存储器软错误率降低至10^-18次/比特·小时(JEDEC标准)。

- 刷新电路:DRAM每64ms执行全阵列刷新,电荷保持时间随温度上升呈指数下降,85℃时需缩短至32ms(美光科技白皮书)。

- 温度补偿:动态调整刷新频率与操作电压,确保-40℃至125℃工业级温度范围内的数据完整性。

主流存储矩阵类型对比

| 类型 | 单元结构 | 读写速度 | 非易失性 | 典型应用场景 |

|---|---|---|---|---|

| SRAM | 6晶体管锁存器 | 1ns | 否 | CPU高速缓存 |

| DRAM | 1T1C | 10ns | 否 | 主存储器 |

| NOR Flash | 浮栅晶体管 | 100ns | 是 | 嵌入式系统固件 |

| 3D NAND | 垂直电荷陷阱 | 50μs | 是 | SSD固态存储 |

行业前沿技术突破

- 存算一体架构:SK海力士开发HBM-PIM,在存储矩阵内集成计算单元,AI推理能效比提升2.5倍(Hot Chips 2022)。

- 铁电存储器(FeRAM):东芝推出28nm FeRAM,利用铁电材料极化方向存储数据,擦写耐久度达10^14次(IEDM会议报告)。

- 光学存储矩阵:英特尔实验室验证硅光互连存储架构,光信号传输带宽突破10Tb/s(Nature Photonics, 2024)。

技术挑战与发展趋势

当前存储矩阵面临制程微缩带来的量子隧穿效应与信号串扰加剧等问题,行业正探索以下方向:

- 新材料应用:二维材料(如MoS2)构建原子级薄层存储单元

- 先进封装:采用Hybrid Bonding实现3D堆叠互连间距<10μm

- 近存计算:通过存内逻辑运算突破冯·诺依曼瓶颈

引用说明

本文技术参数引用自《半导体存储技术导论》(清华大学出版社)、JEDEC JESD79-4B标准文档及IEEE国际固态电路会议(ISSCC)公开发表论文。