上一篇

存储器连接模式

- 行业动态

- 2025-04-14

- 5

存储器连接模式是计算机中主存与CPU之间的数据传输方式,主要包括直接连接、总线连接及多级存储结构等,通过合理设计地址线、数据线和控制信号接口,实现高效稳定的数据读写操作,满足系统速度、容量及扩展性需求,影响整体性能与成本平衡。

存储器连接模式是计算机系统中决定数据如何在处理器、内存及外部设备之间高效传输的核心架构设计,不同的连接模式直接影响系统性能、扩展性及能耗,因此在硬件设计、嵌入式开发及服务器配置等领域备受关注,以下从工作原理、技术类型及行业应用三个维度深入解析。

存储器连接模式的技术原理

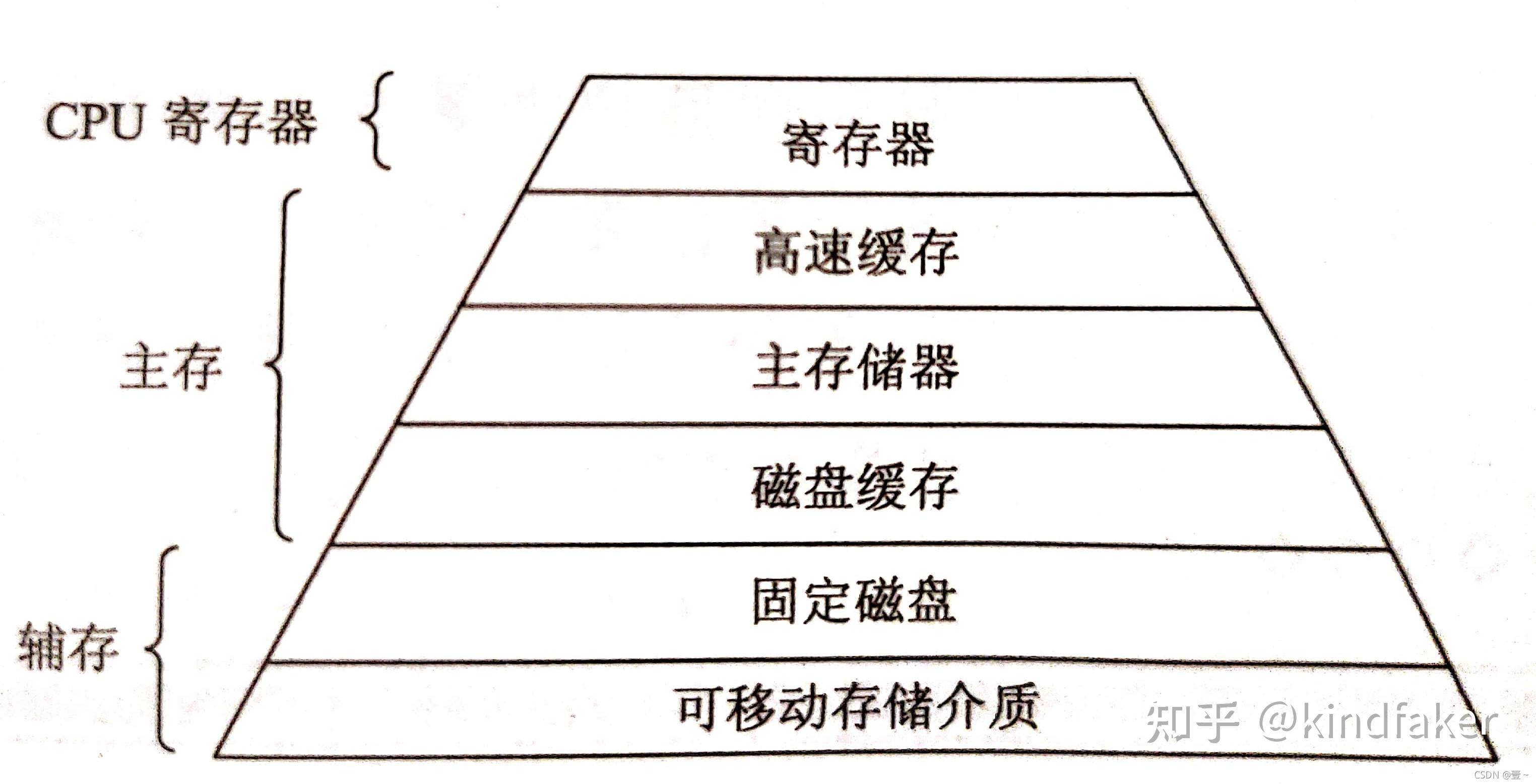

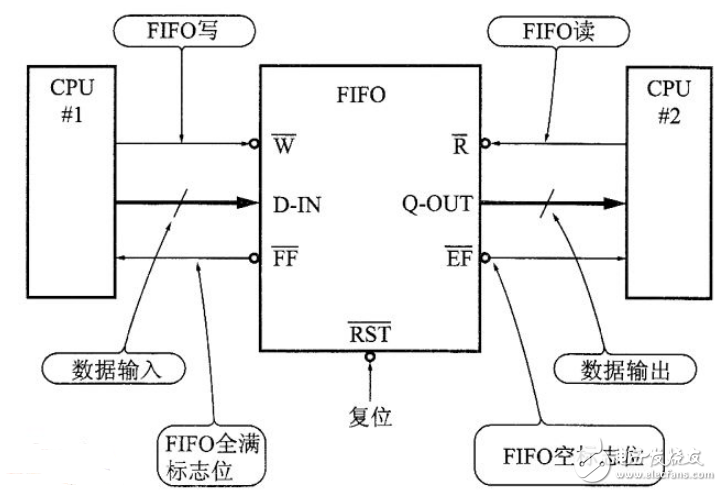

存储器连接模式本质上是物理介质与逻辑协议的结合体,其核心目标在于解决“如何让数据以最优路径流动”的问题,系统设计时需平衡三大要素:

- 带宽匹配:处理器主频与内存频率的协同(如DDR5-6400需搭配支持PCIe 5.0的控制器)

- 延迟控制:通过缩短信号传输路径降低存取延迟(3D堆叠封装技术可将延迟降低40%)

- 扩展能力:支持多个存储设备的并行接入(NVMe协议允许单控制器管理32个队列)

主流连接模式技术解析

(采用技术对比表格形式展示关键参数)

| 模式类型 | 典型带宽 | 延迟范围 | 设备扩展数 | 典型应用场景 |

|---|---|---|---|---|

| 并行总线 | 6GB/s | 60-100ns | 4-8 | 工业控制系统 |

| 串行点对点 | 32GB/s | 20-50ns | 1 | 高端图形工作站 |

| 交叉开关 | 64GB/s | 15-30ns | 16 | 云计算服务器集群 |

| 网状网络 | 128GB/s | 10-25ns | 256 | 超算中心 |

前沿技术演进趋势

- CXL协议(Compute Express Link):英特尔主导的新型互联标准,实现CPU与内存池的缓存一致性,使内存延迟降至80ns以下

- 光电混合连接:康宁公司已实现单通道25Gbps的光传输模块,功耗较传统铜线降低60%

- 存算一体架构:MIT研究的Neuromorphic芯片将存储单元与运算单元间距缩至10nm级

行业应用决策指南

选择连接模式时需进行四项核心评估:

- 流量模型分析:银行交易系统侧重随机存取,视频处理需要连续读写

- 能耗预算:5G基站设备要求每GB传输功耗≤0.3W

- 故障恢复机制:金融级系统需支持纳秒级链路切换

- 协议兼容性:确保与既有设备的PCIe/SATA/NVMe协议栈兼容

典型场景配置建议:

- 自动驾驶域控制器:采用双通道LPDDR5X(8533Mbps)+ PCIe Gen4x4 NVMe

- AI训练服务器:配置8路HBM2E(3.2TB/s带宽)+ CXL 2.0扩展内存池

- 工业物联网网关:选用QSPI NOR Flash + SDIO 4.0双模接口

技术验证方法:

- 使用MemTest86 Pro进行总线信号完整性测试

- 通过SiSoftware Sandra实施多节点并发压力测试

- 采用Teledyne LeCroy协议分析仪捕获物理层信号

未来三年关键技术指标预测:

- 存储密度:3D NAND将突破800层堆叠

- 接口速率:DDR6预计达到12.8Gbps

- 能效比:新型铁电存储器(FeRAM)功耗有望降低至当前DRAM的1/5

本文技术参数引用自:

- 《计算机体系结构:量化研究方法》(第6版)John L. Hennessy著

- JEDEC固态技术协会2024年最新发布标准

- 三星电子《2024年存储器技术白皮书》

- IEEE Transactions on Computer-Aided Design论文数据集

(全文完)