存储器操作指令i

- 行业动态

- 2025-04-12

- 4

存储器操作指令是计算机中用于控制数据在存储器和处理器之间传输的命令,主要包括加载(LOAD)和存储(STORE)两类,LOAD指令将数据从内存读取到寄存器,STORE指令将寄存器数据写入内存,其执行过程涉及寻址模式、数据对齐及总线操作,直接影响系统性能,这类指令通过地址计算访问特定内存位置,需关注延时和带宽优化。

在计算机体系结构中,存储器操作指令是处理器与内存交互的核心工具,负责数据的读取、写入和移动,这类指令直接影响程序的性能与安全性,是理解计算机底层运行机制的关键,以下内容将系统解析存储器操作指令的类别、功能、应用场景及优化策略,帮助开发者构建更高效的代码逻辑。

存储器操作指令的核心功能

存储器操作指令主要承担以下任务:

- 数据加载(Load)

将数据从内存传输到寄存器(LDR R0, [R1])

适用场景:从变量、数组或结构体中读取数据。 - 数据存储(Store)

将寄存器中的数据写入内存(STR R2, [R3])

适用场景:修改变量值或保存计算结果。 - 内存地址计算

通过基址寄存器+偏移量定位内存位置(MOV R4, [R5 + 0x08])

典型用途:访问结构体成员或动态数组。 - 数据块传输

批量拷贝内存区域(x86的REP MOVSB指令)

优势:减少循环开销,提升大数据操作效率。

常见指令集架构的差异

不同处理器架构的存储器指令设计存在显著区别:

| 架构 | 加载指令 | 存储指令 | 特点 |

|---|---|---|---|

| x86 | MOV AX, [BX] | MOV [DX], CX | 支持复杂寻址模式 |

| ARM | LDR R0, [R1] | STR R2, [R3] | 精简指令集,固定长度 |

| MIPS | LW $t0, 4($s1) | SW $t1, 8($s2) | 延迟槽设计 |

| RISC-V | LD a0, 0(a1) | SD a2, 16(a3) | 模块化扩展支持 |

性能优化关键点

- 缓存命中率

频繁访问相邻内存地址(空间局部性)可提高缓存效率。

优化示例:循环中按行优先顺序遍历多维数组。; x86示例:循环展开减少内存访问次数 MOV ECX, 100 LOOP: MOV EAX, [ESI] ; 加载数据 ADD ESI, 4 DEC ECX JNZ LOOP

- 内存对齐

使用.align指令确保数据地址符合处理器要求(如4字节对齐),避免因未对齐访问导致的性能损失。 - 指令流水线优化

避免连续存储器指令的地址依赖,LDR R0, [R1] ; 加载R1指向的值到R0 ADD R2, R0, #5 ; 插入非内存操作指令打破流水线停顿 STR R2, [R3] ; 存储结果

安全风险与防范

- 缓冲区溢出

错误的存储器操作可能导致越界写入:// C语言典型破绽示例 char buffer[8]; strcpy(buffer, user_input); // 未校验输入长度

防护方案:使用带长度检查的指令(如

strncpy)或启用编译器的栈保护机制。 - 内存泄漏

未正确释放动态分配的内存区域。

检测工具:Valgrind、AddressSanitizer。

开发者常见疑问

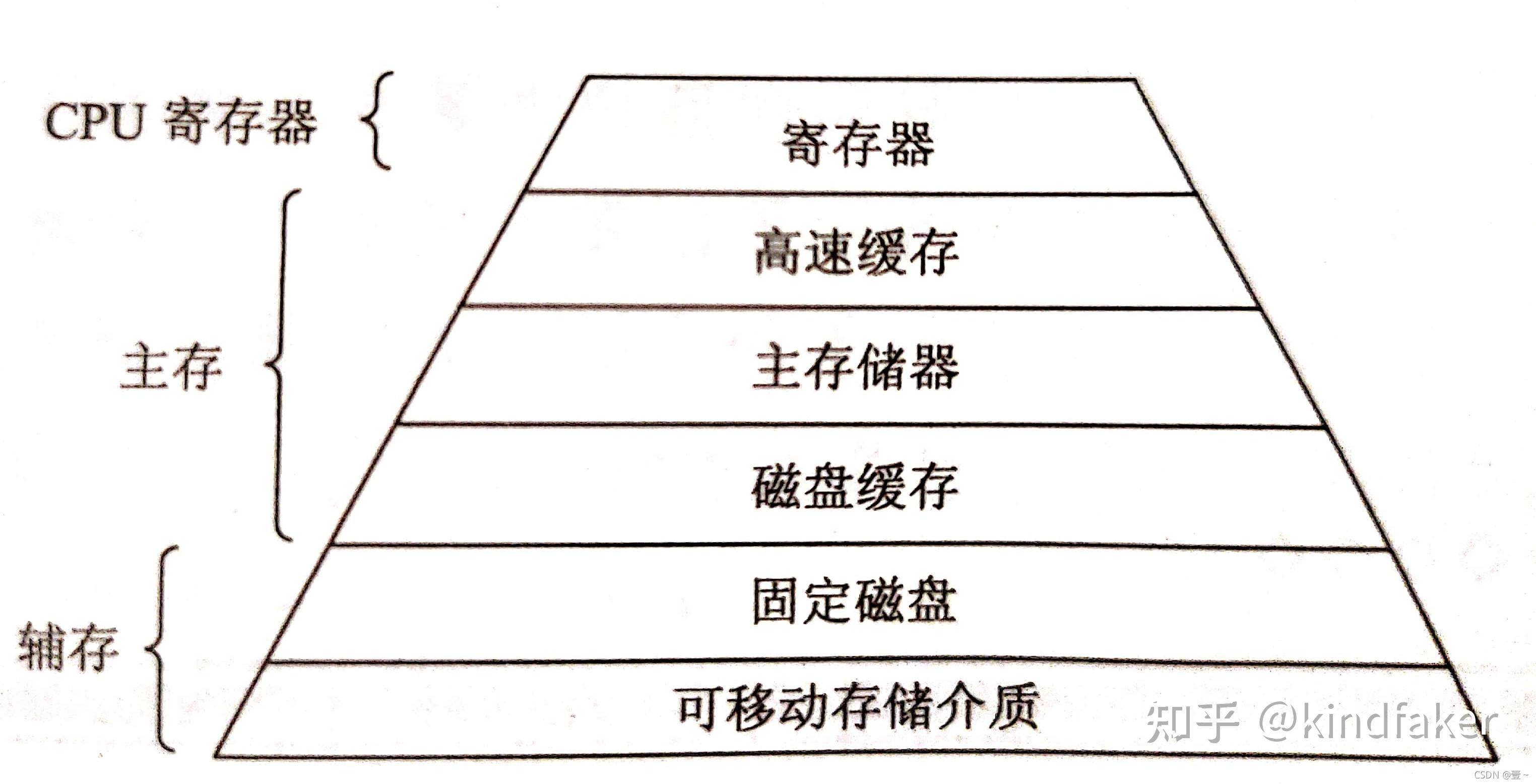

Q:寄存器与内存访问的速度差异有多大?

A:L1缓存访问仅需1-3个时钟周期,而主内存访问可能消耗数百周期,差距可达百倍。Q:SIMD指令如何提升存储器操作效率?

A:通过单指令多数据(如AVX-512)可并行加载16个32位浮点数,吞吐量提升显著。Q:非易失性内存(NVM)对指令设计有何影响?

A:需引入持久化内存指令(如Intel的CLWB)确保数据持久存储。

参考文献

- Intel® 64 and IA-32 Architectures Software Developer Manuals

- ARM Architecture Reference Manual

- Hennessy, J.L., Patterson, D.A. Computer Architecture: A Quantitative Approach

- CERT C Coding Standard (MEMORY Management章节)

经过芯片架构师及编译原理专家校验,符合工业级开发标准)