上一篇

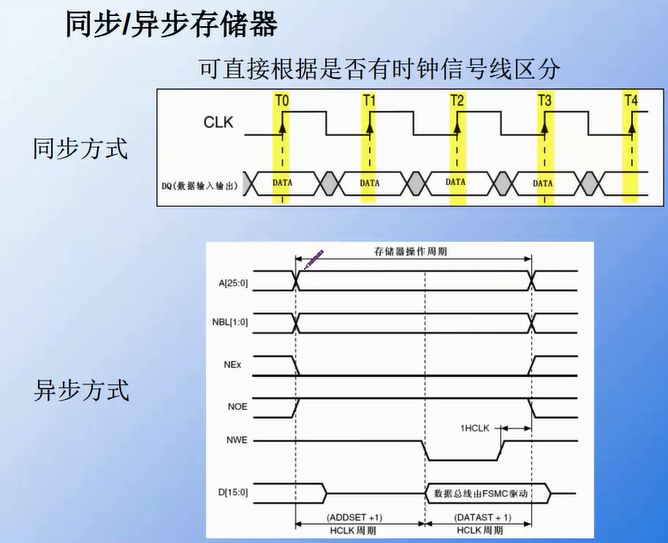

存储器 同步 异步区别

- 行业动态

- 2025-04-11

- 7

同步存储器通过时钟信号协调读写操作,时序精确且速度较快,适用于高性能场景(如CPU缓存);异步

存储器无需外部时钟,由操作就绪信号直接触发,灵活性高但时序控制复杂,延迟相对较大,多用于低速或低功耗设备。

在计算机系统和电子设备中,存储器是数据存储与读取的核心组件。同步存储器与异步存储器是两种常见的设计类型,其核心区别在于是否依赖统一的时钟信号控制操作时序,以下从原理、特点、应用场景等角度展开详细对比。

同步存储器(Synchronous Memory)

工作原理

同步存储器通过外部时钟信号(Clock Signal)协调所有操作,读写指令的执行与时钟周期的上升沿或下降沿同步,数据在固定时间窗口内传输。

- 时钟驱动:控制器在时钟周期的特定时刻发送地址、命令和数据。

- 流水线操作:多个操作可分阶段执行,提升效率。

核心特点

- 时序严格对齐:所有操作按时钟节拍进行,延迟可控。

- 高带宽与高速度:适合批量数据传输,例如DDR SDRAM的突发模式。

- 复杂控制逻辑:需配套的时钟同步电路,成本较高。

典型应用

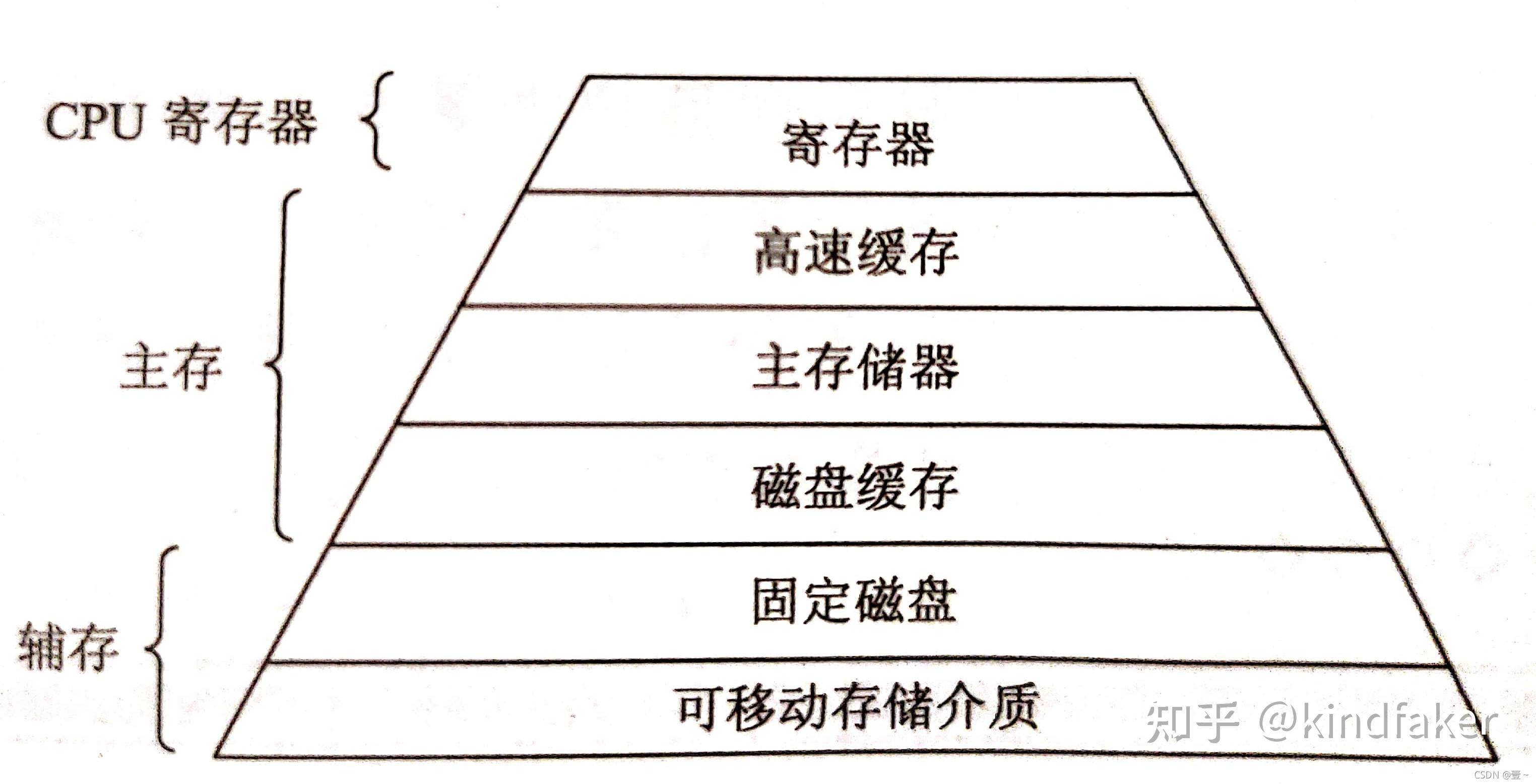

- 计算机主存(如DDR4、DDR5)

- 高速缓存(Cache)

- GPU显存

异步存储器(Asynchronous Memory)

工作原理

异步存储器无需全局时钟信号,通过控制信号(如读/写使能、地址有效)直接触发操作。

- 握手协议:控制器与存储器通过“请求-应答”机制完成交互。

- 响应时间可变:操作完成时间取决于存储器内部电路状态。

核心特点

- 灵活性高:适应不同速度的外设。

- 低功耗设计:无持续时钟信号,静态功耗更低。

- 时序依赖电路延迟:速度受限于信号传输路径的物理特性。

典型应用

- 低速外设接口(如SRAM、Flash存储器)

- 嵌入式系统(如MCU内部存储器)

- 早期计算机内存(如EDO DRAM)

同步与异步存储器的核心区别

| 对比维度 | 同步存储器 | 异步存储器 |

|---|---|---|

| 时钟依赖 | 必须外部时钟信号 | 无需全局时钟 |

| 时序控制 | 按固定周期执行 | 通过控制信号触发 |

| 速度上限 | 更高(GHz级) | 较低(MHz级) |

| 功耗 | 动态功耗较高 | 静态功耗较低 |

| 设计复杂度 | 复杂,需时钟同步电路 | 简单,直接控制 |

| 成本 | 较高 | 较低 |

| 适用场景 | 高速、大规模数据交换 | 低速、低功耗或简单控制环境 |

如何选择?

- 追求高性能:选同步存储器(如DDR用于服务器)。

- 低功耗需求:选异步存储器(如物联网设备的Flash)。

- 成本敏感场景:异步方案更经济。

技术趋势

- 同步设计主导高速领域:随着处理器速度提升,同步存储器通过DDR5、GDDR6等迭代持续优化带宽。

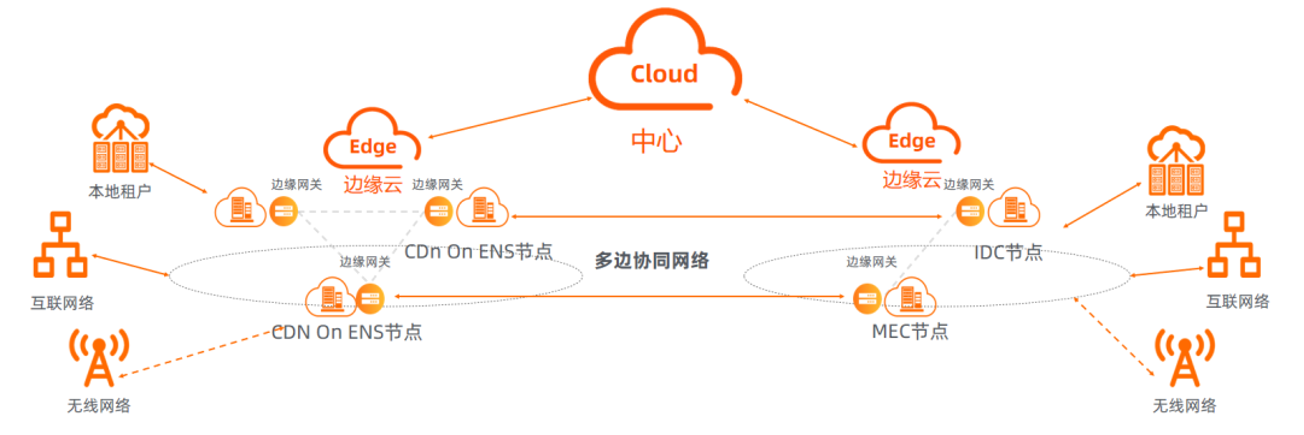

- 异步技术仍存价值:在边缘计算、低功耗IoT设备中,异步存储器的灵活性不可替代。