上一篇

存储器周期

- 行业动态

- 2025-04-11

- 5

存储器周期指存储器完成一次完整读写操作所需时间,包括地址建立、数据传输及恢复阶段,通常分为读取周期和写入周期,涵盖信号稳定、数据存取等步骤,周期时间直接影响存储器性能,较短的周期可提升系统运行速度,是衡量存储设备工作效能的重要参数。

什么是存储器周期?

存储器周期(Memory Cycle)指存储器完成一次完整操作所需的时间,通常包含地址建立、数据读写、恢复三个阶段,当CPU向内存发起读取请求时,存储器需要:

- 地址建立:接收并锁定目标地址;

- 数据读取/写入:根据地址找到对应存储单元,传输数据;

- 恢复:为下一次操作重置状态。

整个过程的总耗时即为存储器周期,单位为纳秒(ns)或兆赫兹(MHz)。

存储器周期的组成

不同存储器的周期细节差异较大,但核心步骤可归纳为:

- 存取时间(Access Time):从地址确认到数据输出的耗时;

- 恢复时间(Cycle Time):完成操作后,存储单元恢复稳定状态的时间;

- 预充电时间(Precharge Time):动态存储器(如DRAM)需补充电荷以保持数据,此过程计入周期。

以DRAM为例,其周期可能包含多次预充电,因此周期时间通常比存取时间长20%-50%。

不同类型存储器的周期对比

| 存储器类型 | 典型周期时间 | 特点 | 应用场景 |

|---|---|---|---|

| SRAM | 10-50 ns | 无需刷新,速度快,成本高 | 高速缓存(CPU缓存) |

| DRAM | 50-100 ns | 需刷新,密度高,成本低 | 主内存(电脑内存条) |

| Flash | 100μs-1ms | 非易失性,擦写次数有限 | SSD、U盘 |

| ROM | 50-200 ns | 只读,稳定性高 | 固件存储 |

存储器周期对系统性能的影响

瓶颈效应

CPU运算速度远高于存储器周期,若周期过长,CPU会因等待数据而闲置(称为“内存墙”问题),1 GHz的CPU每秒可处理10亿条指令,但若存储器周期为100 ns,则每秒最多完成1000万次访问,两者速度差距可达百倍。多级缓存设计

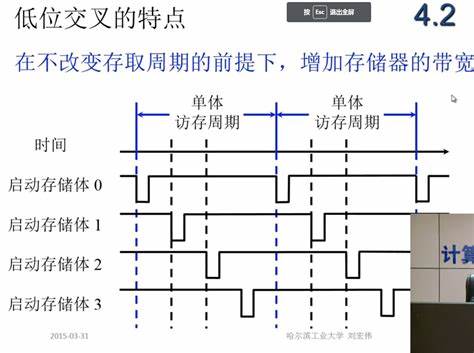

为缓解性能瓶颈,现代计算机采用多级缓存(L1/L2/L3),L1缓存使用SRAM,周期仅1-3 ns,但容量小;主存使用DRAM,周期较长,但容量更大。并行技术

通过交叉存储(Interleaving)或双通道技术,存储器可并行处理多个请求,双通道DRAM的带宽提升近一倍,有效缩短平均周期。

如何优化存储器周期?

硬件层面

- 选择低延迟存储器(如GDDR6显存周期仅12-18 ns);

- 增加总线位宽(64位升级至128位);

- 采用3D堆叠技术(如HBM2缩短信号传输距离)。

软件层面

- 优化数据局部性(利用空间局部性预取数据);

- 减少冗余访问(通过缓存算法如LRU);

- 异步编程(避免阻塞式读写)。

未来趋势:突破存储墙

随着AI和超算对带宽需求的爆炸式增长,存储器周期优化成为研究热点,新型技术如:

- 存算一体(In-Memory Computing):直接在存储单元内计算,减少数据传输;

- 光互连存储器:用光子代替电子传输信号,延迟降至皮秒级;

- MRAM/ReRAM:非易失+纳秒级读写,可能替代部分DRAM/SRAM。

引用说明

- Patterson, D. A., & Hennessy, J. L. (2017). Computer Organization and Design: The Hardware/Software Interface. Elsevier.

- JEDEC固态技术协会. (2024). DDR5 SDRAM标准.

- IEEE Transactions on Computers. (2021). 存算一体架构的性能分析.